小数分频频率合成器的理论基础 A

Marqu es _, M

Stey aert and W

Sansen ESAT-MICAS, K

Leuven, Kard

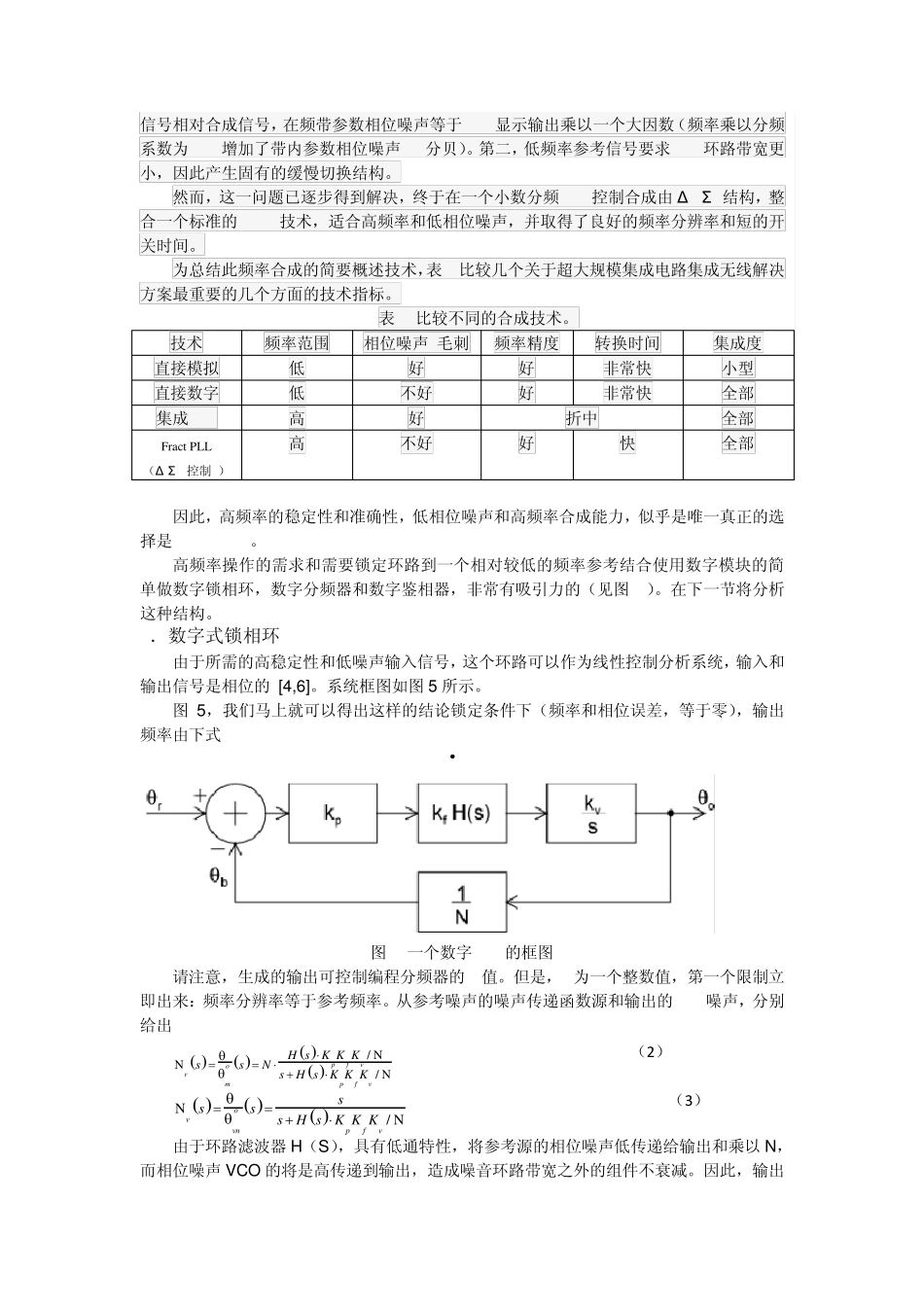

Mercierlaan 94, B-3001 Heverlee, Belgium 本文提出了一种基于锁相回路(PLL)频率合成器的演变概述

数字 PLL 的主要限制的描述,以及随之而来的小数N 技术使用的必要性是有道理的

合成频率的旁瓣典型的杂散噪声线的起源进行了解释

它通过使用数字调制器来控制分频值展示了如何消除这些杂散噪声线

最后,数字调制器的使用同分数N PLL 的输出相位噪声的影响一起进行了分析

介绍 无线通信领域,在过去十年中有了很大的发展

这种快速发展,主要是通过引进强大的数字信号处理技术

这些技术允许执行复杂的调制解调方案,以及先进的数字校正技术,最终产生非常高性能的系统,可以完全或几乎完全集成在一个标准的低成本技术

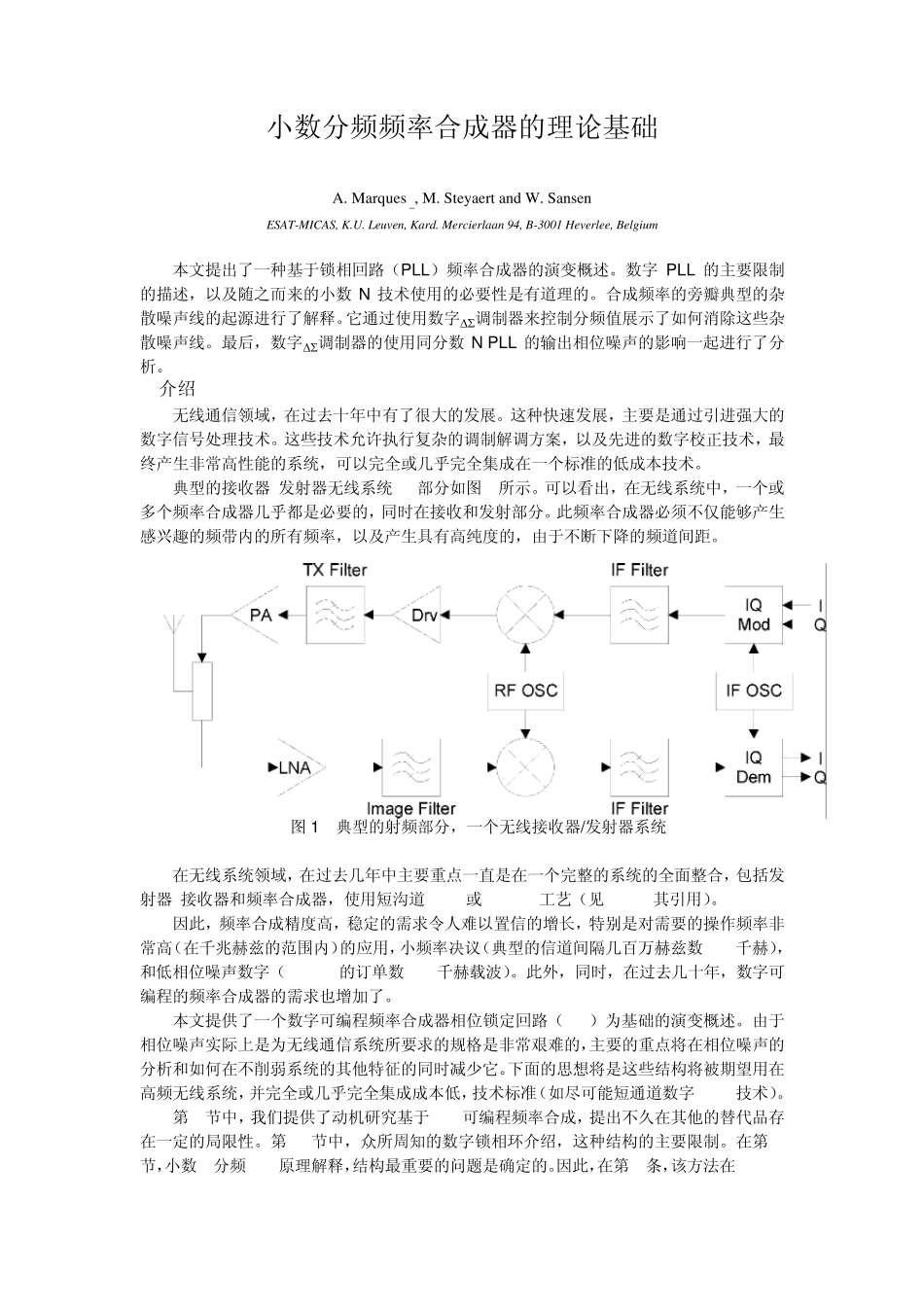

典型的接收器/发射器无线系统 RF部分如图 1所示

可以看出,在无线系统中,一个或多个频率合成器几乎都是必要的,同时在接收和发射部分

此频率合成器必须不仅能够产生感兴趣的频带内的所有频率,以及产生具有高纯度的,由于不断下降的频道间距

图 1 典型的射频部分,一个无线接收器/发射器系统 在无线系统领域,在过去几年中主要重点一直是在一个完整的系统的全面整合,包括发射器/接收器和频率合成器,使用短沟道 CMOS或 BiCMOS工艺(见[1,13]其引用)

因此,频率合成精度高,稳定的需求令人难以置信的增长,特别是对需要的操作频率非常高(在千兆赫兹的范围内)的应用,小频率决议(典型的信道间隔几百万赫兹数100千赫),和低相位噪声数字(100dBc的订单数100千赫载波)

此外,同时,在过去几十年,数字可编程的频率合成器的需求也增加了

本文提供了一个数字可编程频