摄像头视频采集系统的设计与实现 徐宏亮 2012

27 系统采用AD9883a 芯片将摄像头视频信号数字化;然后利用FPGA 芯片进行信号处理,增加行列场有效信号;最后,采用ADV7123 芯片将数字信号转为模拟信号,在本地的显示器输出

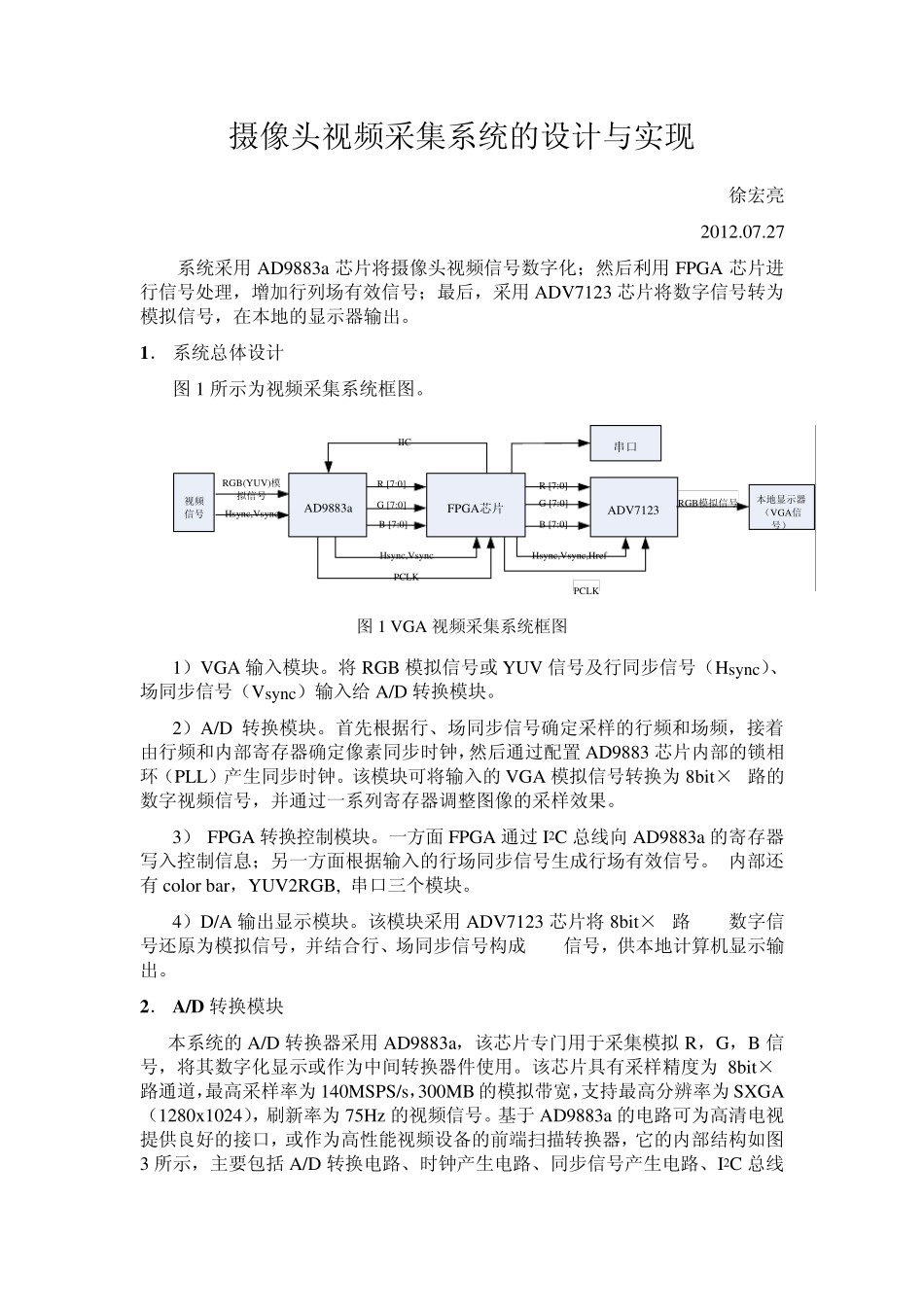

1. 系统总体设计 图1 所示为视频采集系统框图

FPGA芯片ADV7123本地显示器(VGA信号)视频信号RGB(YUV)模拟信号Hsync,VsyncR [7:0]G [7:0]B [7:0]RGB模拟信号Hsync,VsyncPCLKPCLKR [7:0]G [7:0]B [7:0]IICHsync,Vsync,Href串口AD9883a图1 VGA 视频采集系统框图 1)VGA 输入模块

将RGB 模拟信号或YUV 信号及行同步信号(Hsync)、场同步信号(Vsync)输入给A/D 转换模块

2)A/D 转换模块

首先根据行、场同步信号确定采样的行频和场频,接着由行频和内部寄存器确定像素同步时钟,然后通过配置AD9883 芯片内部的锁相环(PLL)产生同步时钟

该模块可将输入的VGA 模拟信号转换为8bit×3路的数字视频信号,并通过一系列寄存器调整图像的采样效果

3) FPGA 转换控制模块

一方面 FPGA 通过I2C 总线向 AD9883a 的寄存器写入控制信息;另一方面根据输入的行场同步信号生成行场有效信号

内部还有color bar,YUV2RGB, 串口三个模块

4)D/A 输出显示模块

该模块采用ADV7123 芯片将8bit×3路 RGB数字信号还原为模拟信号,并结合行、场同步信号构成 VGA信号,供本地计算机显示输出

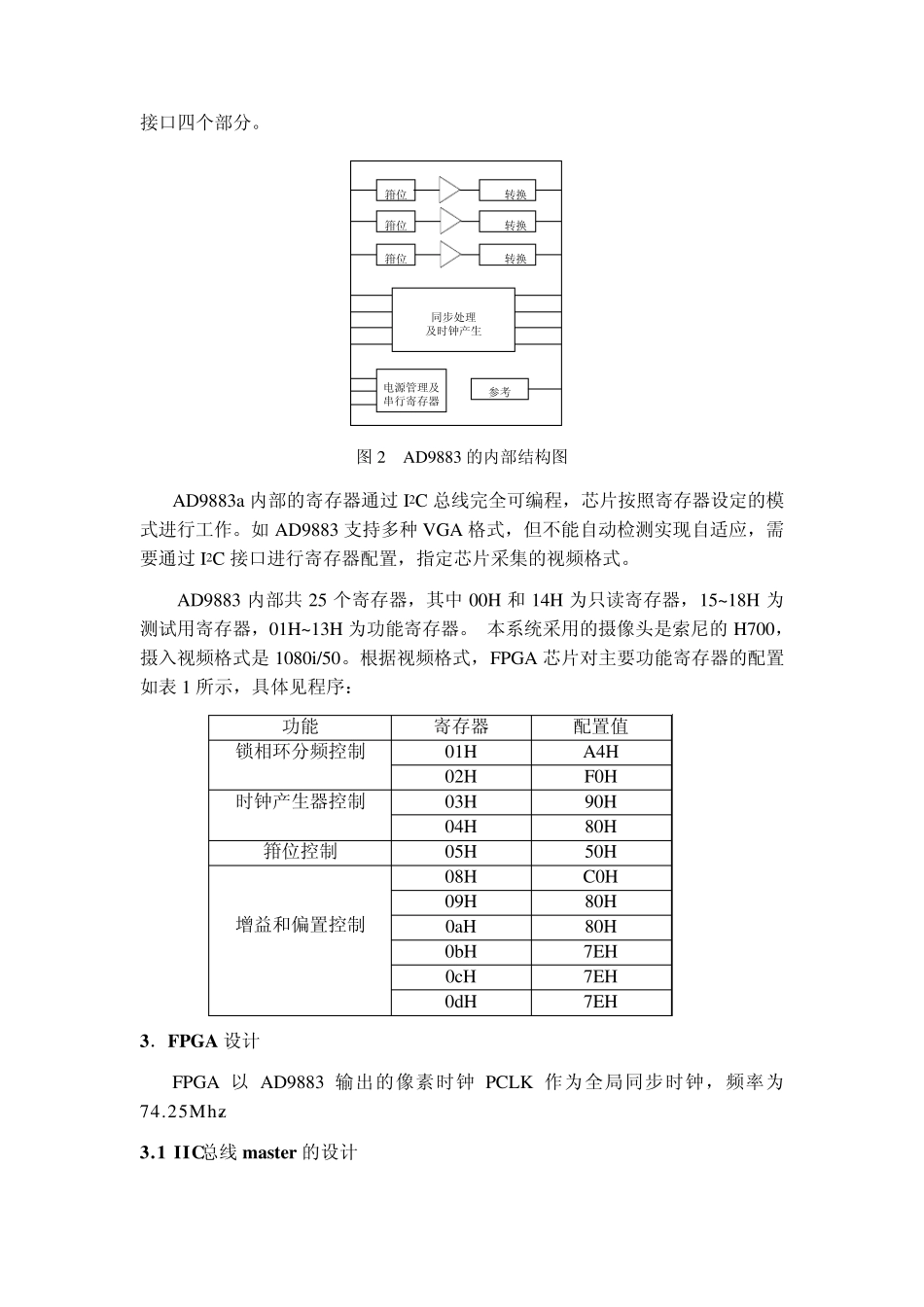

2. A /D 转换模块 本系统的A/D 转换器采用AD9883a,该芯片专门用于采集模拟R,G,B 信号,将其数字化显示或作为中间转换器件使用

该芯片具有采样精度为8bit×3