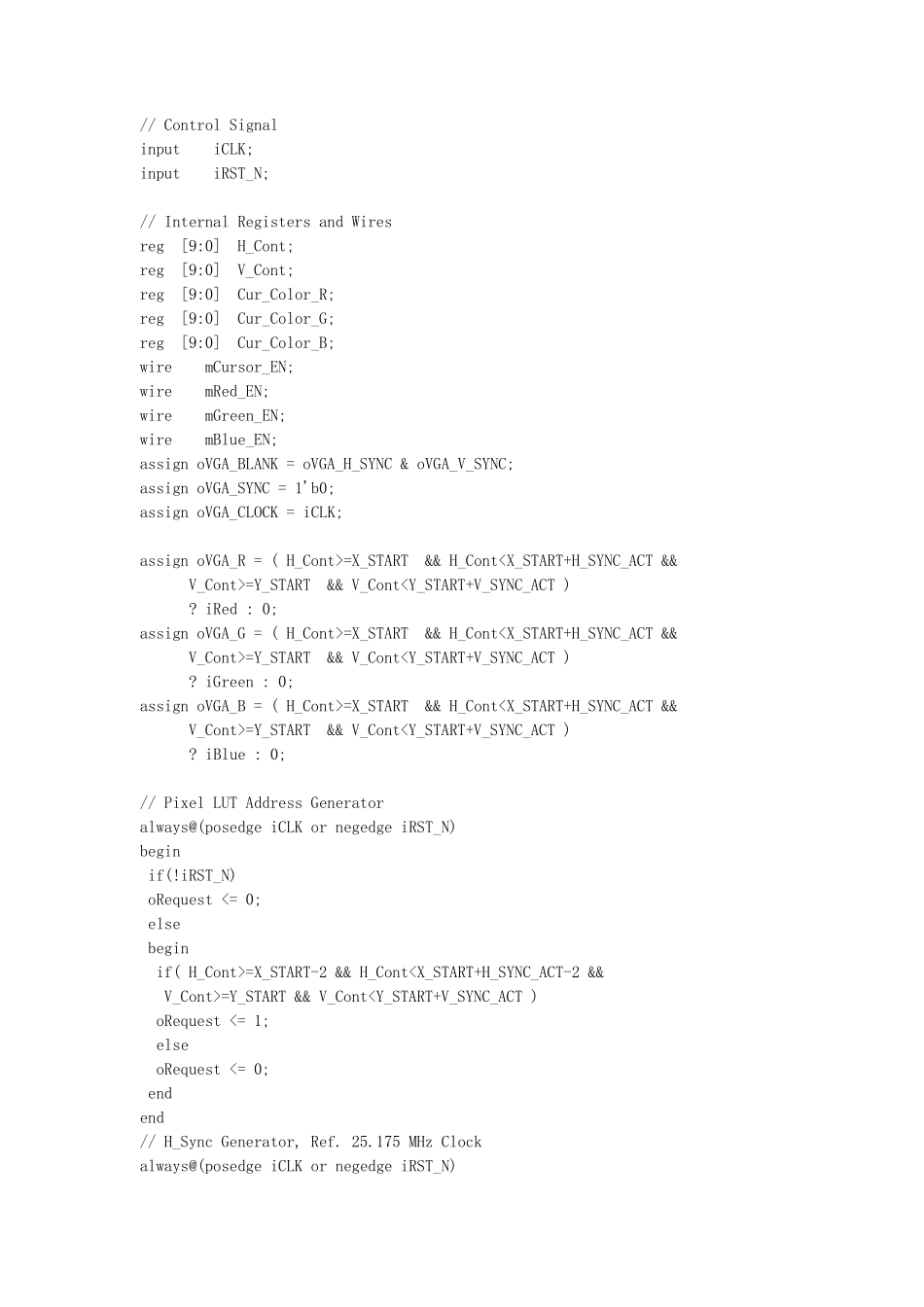

用v erilog 编写fpga 的v ga 显示(z) VGA工业标准是640x480x60Hz,主要有5个信号,即三个颜色信号R/G/B、行同步信号HS和场同步信号VS。 它是从左上角开始一行接一行的扫描,扫描完一屏后又回到左上角扫描。 标准要求是场频 59.94Hz,行频 31469Hz,时钟频率 25.175MHz 这是Altera的DE2开发板上自带的演示程序。可以先搜一下 VGA工业标准的时序图,再看这个代码就会很简单, 就不注释了。弄清楚行同步、场同步、前肩、后肩,一切都 easy module VGA_Controller( // Host Side iRed, iGreen, iBlue, oRequest, // VGA Side oVGA_R, oVGA_G, oVGA_B, oVGA_H_SYNC, oVGA_V_SYNC, oVGA_SYNC, oVGA_BLANK, oVGA_CLOCK, // Control Signal iCLK, iRST_N ); `include "VGA_Param.h" // Host Side input [9:0] iRed; input [9:0] iGreen; input [9:0] iBlue; output reg oRequest; // VGA Side output [9:0] oVGA_R; output [9:0] oVGA_G; output [9:0] oVGA_B; output reg oVGA_H_SYNC; output reg oVGA_V_SYNC; output oVGA_SYNC; output oVGA_BLANK; output oVGA_CLOCK; // Control Signal input iCLK; input iRST_N; // Internal Registers and Wires reg [9:0] H_Cont; reg [9:0] V_Cont; reg [9:0] Cur_Color_R; reg [9:0] Cur_Color_G; reg [9:0] Cur_Color_B; wire mCursor_EN; wire mRed_EN; wire mGreen_EN; wire mBlue_EN; assign oVGA_BLANK = oVGA_H_SYNC & oVGA_V_SYNC; assign oVGA_SYNC = 1'b0; assign oVGA_CLOCK = iCLK; assign oVGA_R = ( H_Cont>=X_START && H_Cont=Y_START && V_Cont=X_START && H_Cont=Y_START && V_Cont=X_START && H_Cont=Y_START && V_Cont=X_START-2 && H_Cont