- 1 - 第11 章 片内逻辑分析仪工具——ChipScope Pro 11

1 ChipScope Pro 工具介绍 在FPGA 调试阶段,传统的信号分析手段要求在设计时保留一定数量的FPGA 管脚作为测试管脚,这种方法灵活性差,对PCB 布线也有一定的影响

当今先进的FPGA 器件所具有的规模、速度和板级要求使得利用传统逻辑分析方法来调试采用 FPGA 器件进行的设计几乎是不可能的

Xilinx 公司推出的片内逻辑分析仪 ChipScope Pro 能够通过 JTAG 口,实时地读出 FPGA 的所有内部信号,而只需要片内的少量BlockRAM 和逻辑资源,使得逻辑分析灵活方便

ChipScope Pro 是与 ISE 配套使用的,其版本经过了 ChipScope 4

1i,ChipScope 4

2i,ChipScope Pro 5

1i,ChipScope Pro 5

2i 和 ChipScope Pro 6

1i 的升级过程,ChipScope Pro 6

1i 是与 ISE 6

1 配套使用的最新版本

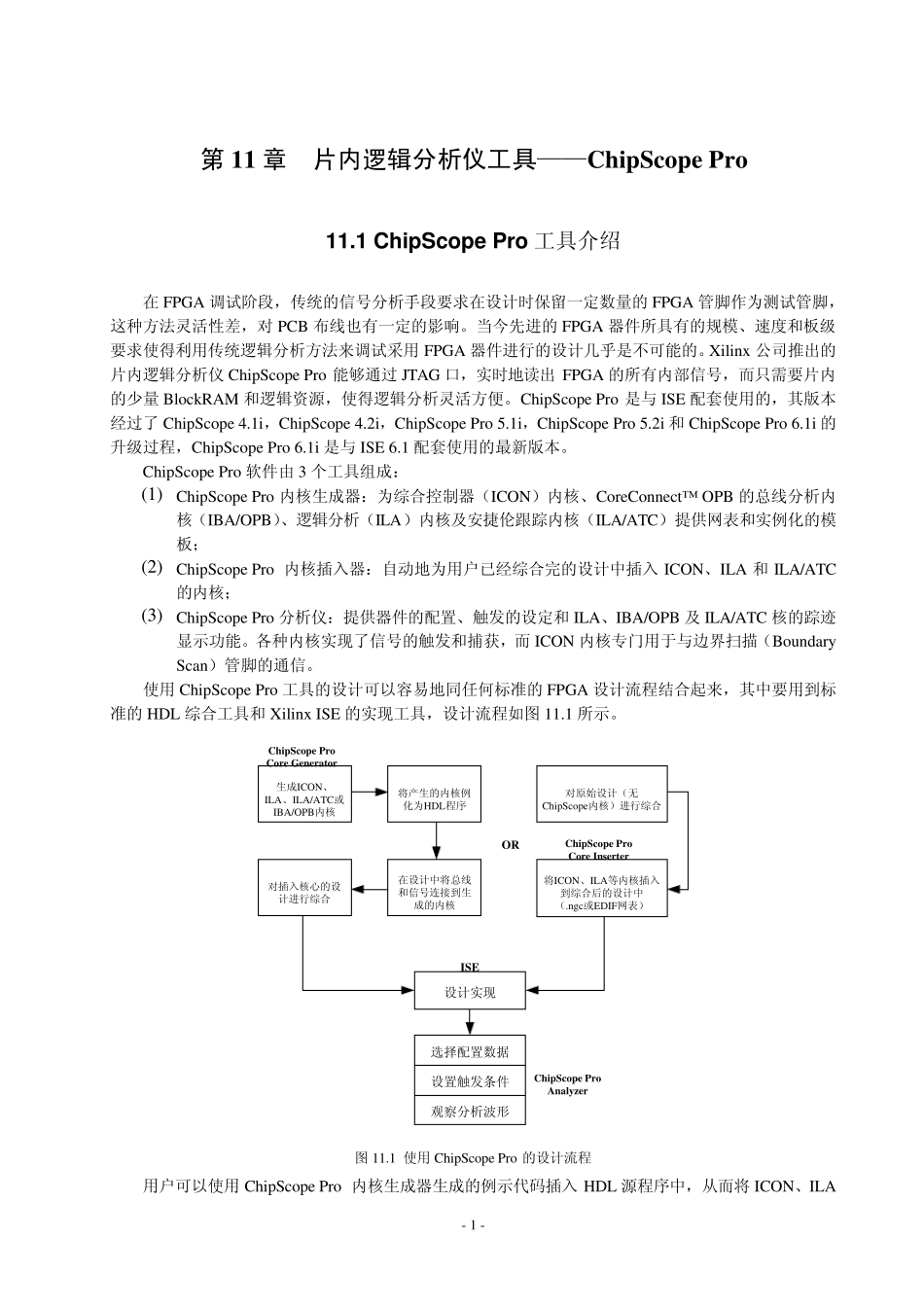

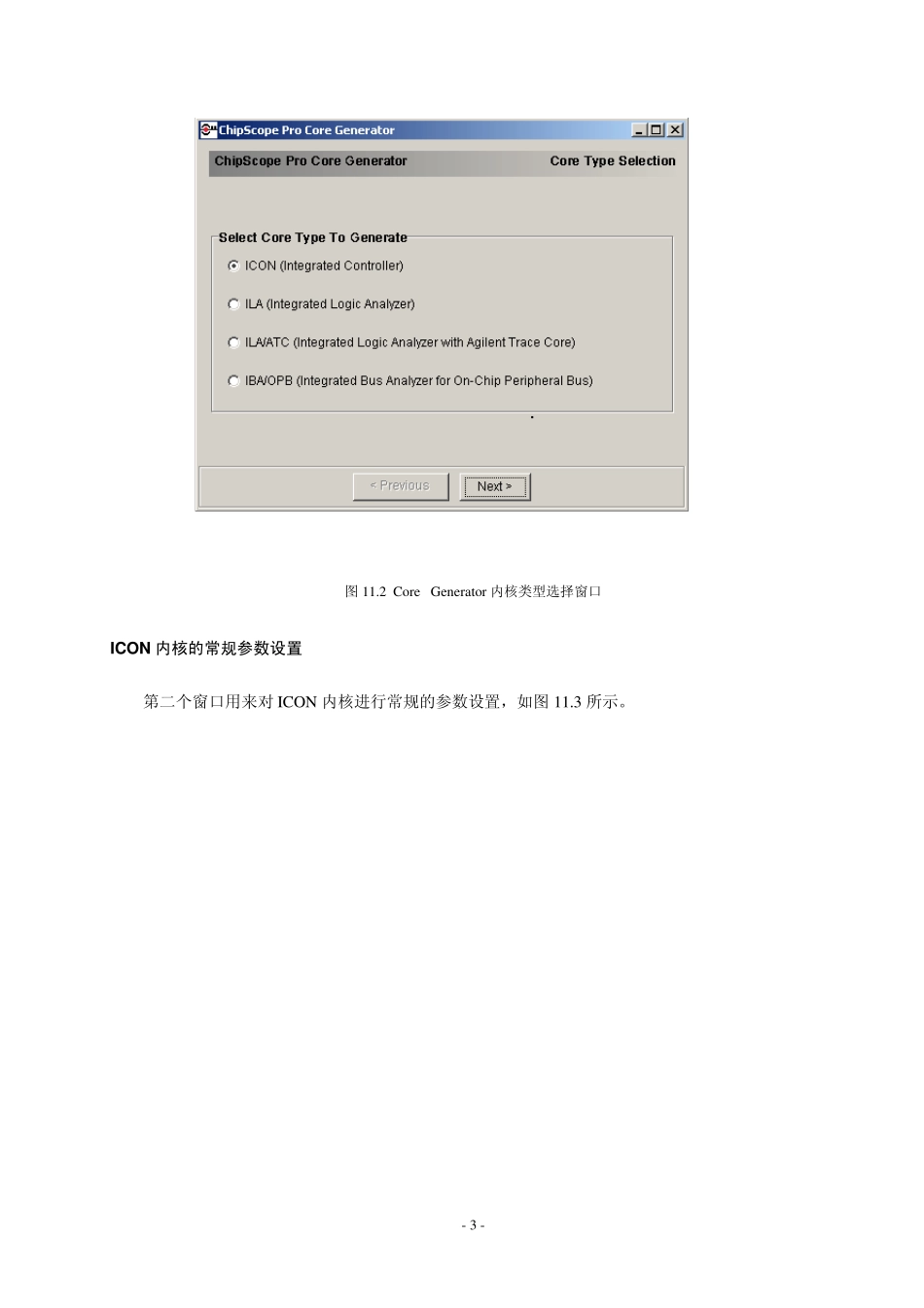

ChipScope Pro 软件由 3 个工具组成: (1) ChipScope Pro 内核生成器:为综合控制器(ICON)内核、CoreConnect™ OPB 的总线分析内核(IBA/OPB)、逻辑分析(ILA)内核及安捷伦跟踪内核(ILA/ATC)提供网表和实例化的模板; (2) ChipScope Pro 内核插入器:自动地为用户已经综合完的设计中插入 ICON、ILA 和 ILA/ATC的内核; (3) ChipScope Pro 分析仪:提供器件的配置、触发的设定和 ILA、IBA/OPB 及 ILA/ATC 核的踪迹显示功能

各种内核实现了信号的触发和捕获,而 ICON 内核专门用于与边界扫描(Boundary Scan)管脚的通信