基于 Verilog HDL 密码锁设计摘 要随着科技的进展数字电路的各种产品广泛应用,传统的机械锁由于其构造的简单,安全性不高,电子密码锁其保密性高,使用灵活性好,安全系数高,使用方便,将会是未来使用的趋势

本设计使用 EDA 设计使设计过程廷到高度自动化,其具有强大的设计功能、测试、仿真分析、管理等功能

使用 EDA 环境完成电路的系统综合设计和仿真

用 VHDL 可以更加快速、灵活地设计出符合各种要求的密码锁

本设计基于 Verilog HDL 语言来设计密码锁,先介绍设计要求和整体设计思想,随后对所使用各模块分别为蜂鸣器模块、显示模块、控制模块、顶层模块进行了介绍,给出各个模块的主要代码,在对各个模块的功能进行仿真

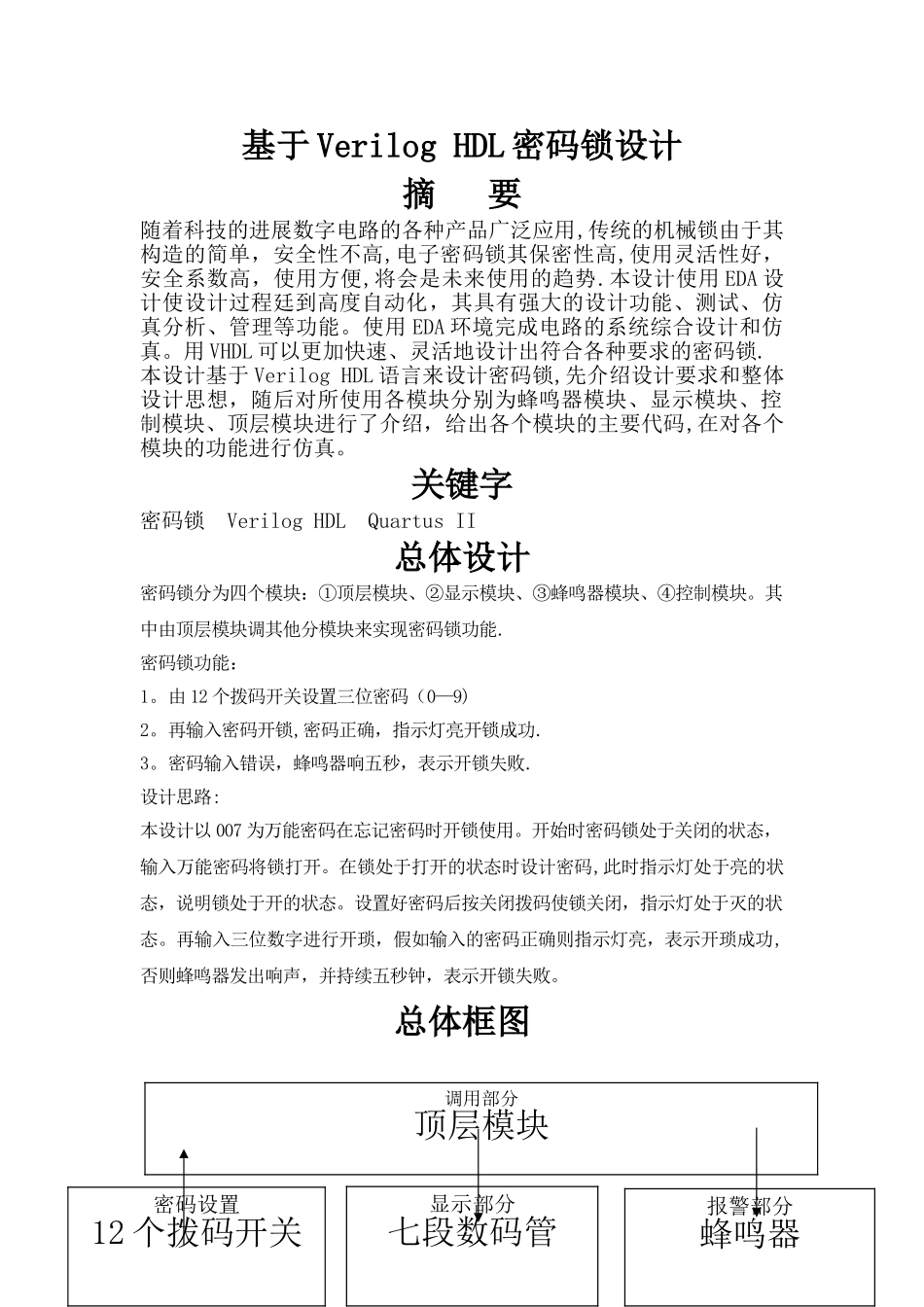

关键字密码锁 Verilog HDL Quartus II总体设计密码锁分为四个模块:①顶层模块、②显示模块、③蜂鸣器模块、④控制模块

其中由顶层模块调其他分模块来实现密码锁功能

密码锁功能:1

由 12 个拨码开关设置三位密码(0—9)2

再输入密码开锁,密码正确,指示灯亮开锁成功

密码输入错误,蜂鸣器响五秒,表示开锁失败

设计思路:本设计以 007 为万能密码在忘记密码时开锁使用

开始时密码锁处于关闭的状态,输入万能密码将锁打开

在锁处于打开的状态时设计密码,此时指示灯处于亮的状态,说明锁处于开的状态

设置好密码后按关闭拨码使锁关闭,指示灯处于灭的状态

再输入三位数字进行开琐,假如输入的密码正确则指示灯亮,表示开琐成功,否则蜂鸣器发出响声,并持续五秒钟,表示开锁失败

总体框图图 1

0 总体框图调用部分顶层模块报警部分蜂鸣器密码设置12 个拨码开关显示部分七段数码管模块功能其及主要代码1

顶层模块实现几个模块的配合工作,它能实现对密码的设置和显示,同时在密码正确时时灯亮,在密码错误时蜂鸣器发出五秒钟的响声

程序如下:module dingceng