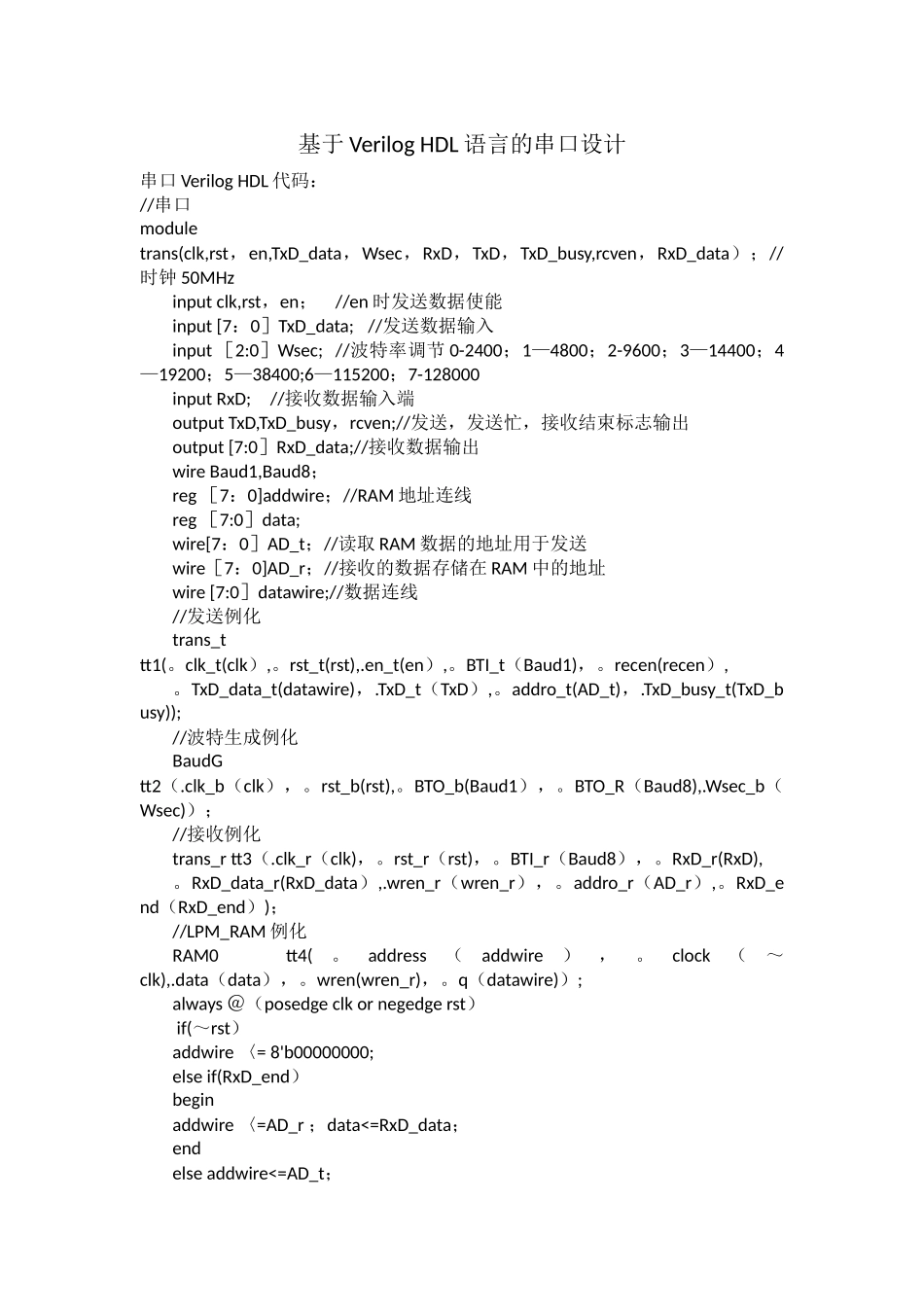

基于 Verilog HDL 语言的串口设计串口 Verilog HDL 代码://串口module trans(clk,rst,en,TxD_data,Wsec,RxD,TxD,TxD_busy,rcven,RxD_data);//时钟 50MHzinput clk,rst,en;//en 时发送数据使能input [7:0]TxD_data; //发送数据输入input [2:0]Wsec; //波特率调节 0-2400;1—4800;2-9600;3—14400;4—19200;5—38400;6—115200;7-128000input RxD;//接收数据输入端output TxD,TxD_busy,rcven;//发送,发送忙,接收结束标志输出output [7:0]RxD_data;//接收数据输出wire Baud1,Baud8;reg [7:0]addwire;//RAM 地址连线reg [7:0]data;wire[7:0]AD_t;//读取 RAM 数据的地址用于发送wire[7:0]AD_r;//接收的数据存储在 RAM 中的地址wire [7:0]datawire;//数据连线//发送例化trans_t tt1(

clk_t(clk),

rst_t(rst),

en_t(en),

BTI_t(Baud1),

recen(recen),

TxD_data_t(datawire),

TxD_t(TxD),

addro_t(AD_t),

TxD_busy_t(TxD_busy));//波特生成例化BaudG tt2(

clk_b(clk),

rst_b(rst),

BTO_b(Baud1),

BTO_R(Baud8),

Wsec_b(Wsec));//接收例化trans_r tt3(

clk_r(clk),

rst_r(rst),

BTI_r(Baud8