摘 要 本课程设计主要内容是利用 EDA 技术设计一个可容纳四组选手的智力竞赛抢答器,全面熟悉、掌握 VHDL 语言基本知识,掌握利用 VHDL 语言对常用的组合逻辑电路和时序逻辑电路编程

本课程设计的开发仿真工具是 MAX+plus II,采纳自顶向下、逐层细化的设计方法设计整套系统,顶层模块用图形描述,底层文件用 VHDL 语言描述

通过波形仿真,实现了智力竞赛抢答器的基本功能,达到了设计要求

关键字 智力竞赛抢答器;EDA 技术;VHDL;MAX+plus II;自顶向下1 引 言 20 世纪 90 年代,引进数字系统设计方法发生突破性变革的技术是VHDL ( Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)

它是一种 IEEE-1076 标准所法律规范的硬件描述语言,主要用于算法级、寄存器级到门级的多种抽象设计层次的数字系统建模,已成为电子设计自动化(EDA)的一种重要手段

本课程设计的主要目的是:全面熟悉、掌握 VHDL 语言基本知识,掌握利用 VHDL 语言对常用的的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效方法,进一步提高上机动手能力,培育设计综合电路的能力,养成编写文档资料的习惯和法律规范编程的思想

2 智力竞赛抢答器的主要功能设计一个 4 人参加的智力竞赛抢答计时器

该系统具有回答问题时间控制的功能,要求回答问题时间小于等于 100 秒(显示为 0~99),时间显示采纳倒计时方式

当达到限定时间时,发出声响以示警告;当有某一参赛者首先按下抢答开关时,相应显示灯亮并伴有声响,此时抢答器不再接受其他输入信号

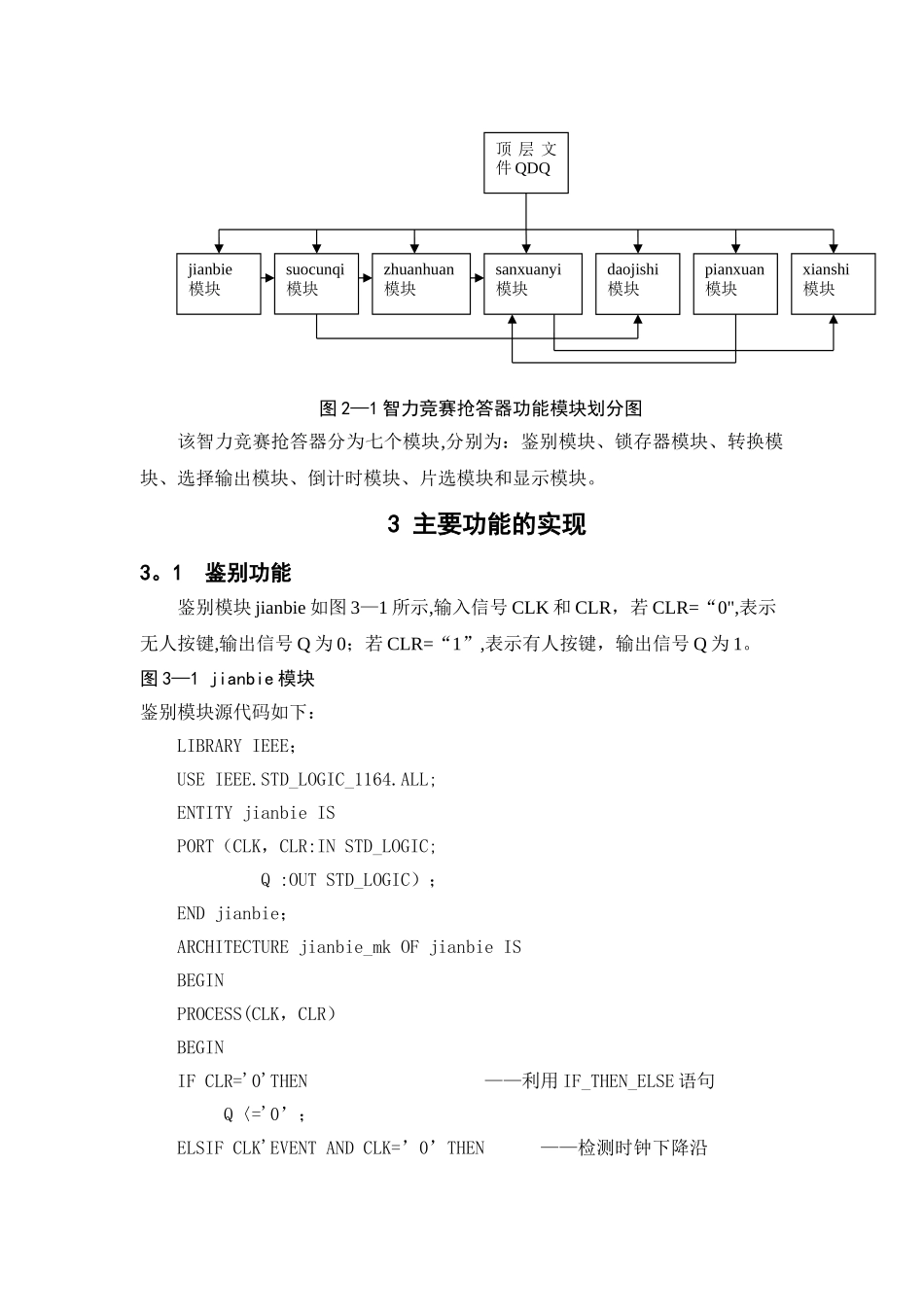

智力竞赛抢答器的功能分块如图 2—1 所示

图 2—1 智力竞赛抢答器功能模块划分图该