数字示波器作者:黄霖宇、陈鹍、侯碧波一等奖作品来源:3A摘要本数字示波器以单片机和 FPGA 为关键,对采样方式的选择和等效采样技术的实现进行了重点设计,使作品不仅具有实时采样方式,并且采用随机等效采样技术实现了运用实时采样速率为 1MHz 的 ADC 进行最大 200MHz 的等效采样

同步系统还具有可测 2mV 小信号、波形存储回放、测频、触发沿选择、校准信号输出等功能

AbstractThis digital oscilloscope takes a MCU and FPGA as the core

We made emphases on the choice of the sampling methods and the implement of equivalent sampling, as a result, our design not only has the real-time sampling mode but also can reach the highest equivalent sample rate of 200 MHz using the real-time sample rate of 1 MHz, by way of random equivalent sampling

At the same time, this system has many other functions, such as 2mV small-signal measuring, storage and re-display of waveform, measuring frequency, selective trigger edge , output of the correction signal and so on

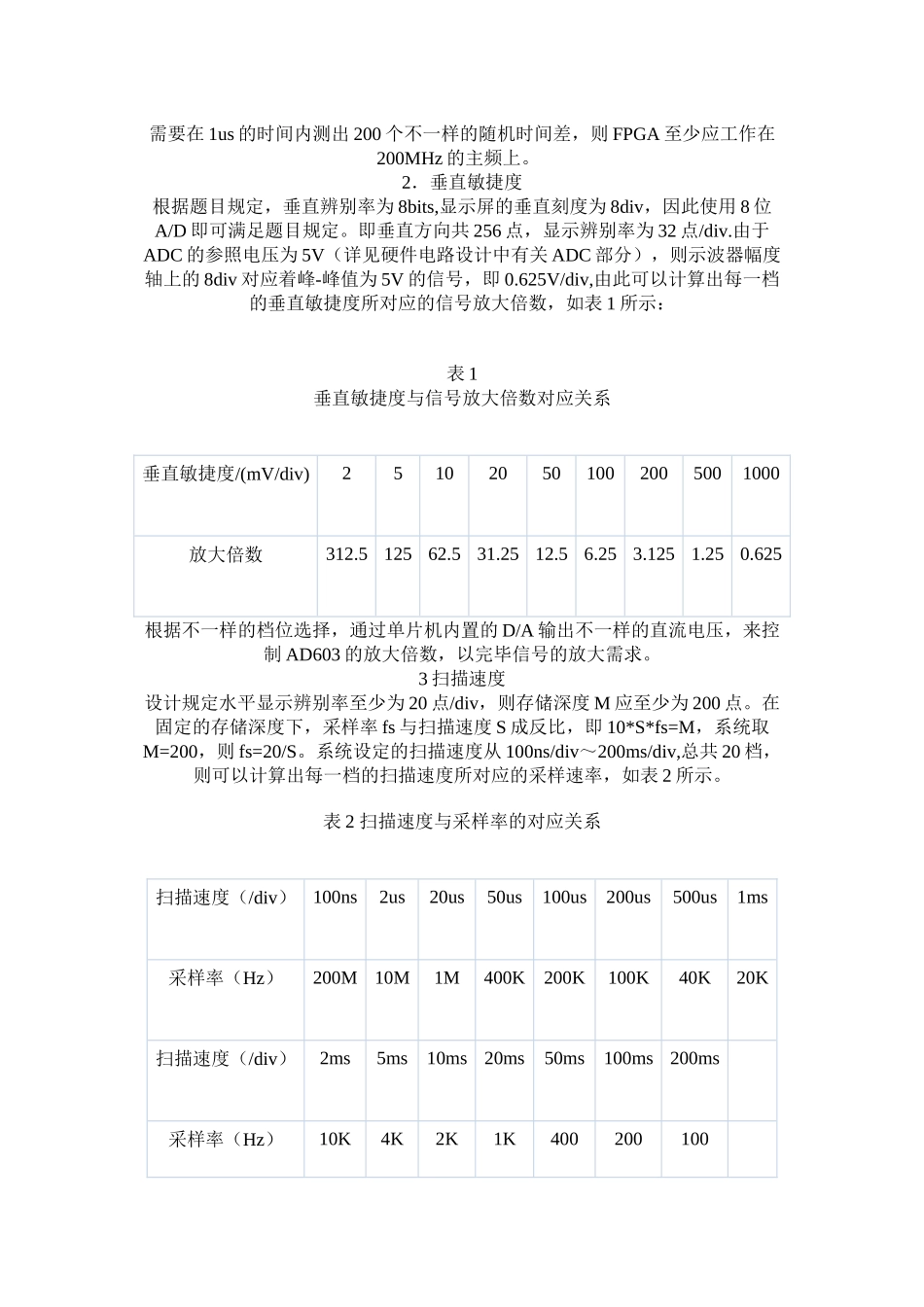

一、总体方案设计1.方案比较与选择仔细分