VHDL ----- Quartus II(11

1 版本)调用 Modelsim 进行仿真之前仿真一直是用 Quartus II 自带的“Vector Waveform File”,但因其功能有限,在老师的推举下接触了 Modelsim,捣腾了一段时间之后总算有所收获了

在查资料的过程中,发现好多二者联合的讲解都是用 Verilog 语言写的例子,而 VHDL 很少

以下是我总结的用 VHDL 语言的具体步骤以与要注意的细节~~坎坷的路就略过了,直接展示成果

例子是‘八位七段数码管的动态扫描显示’一.用 Quartus II 进行 VHDL 语言编译1

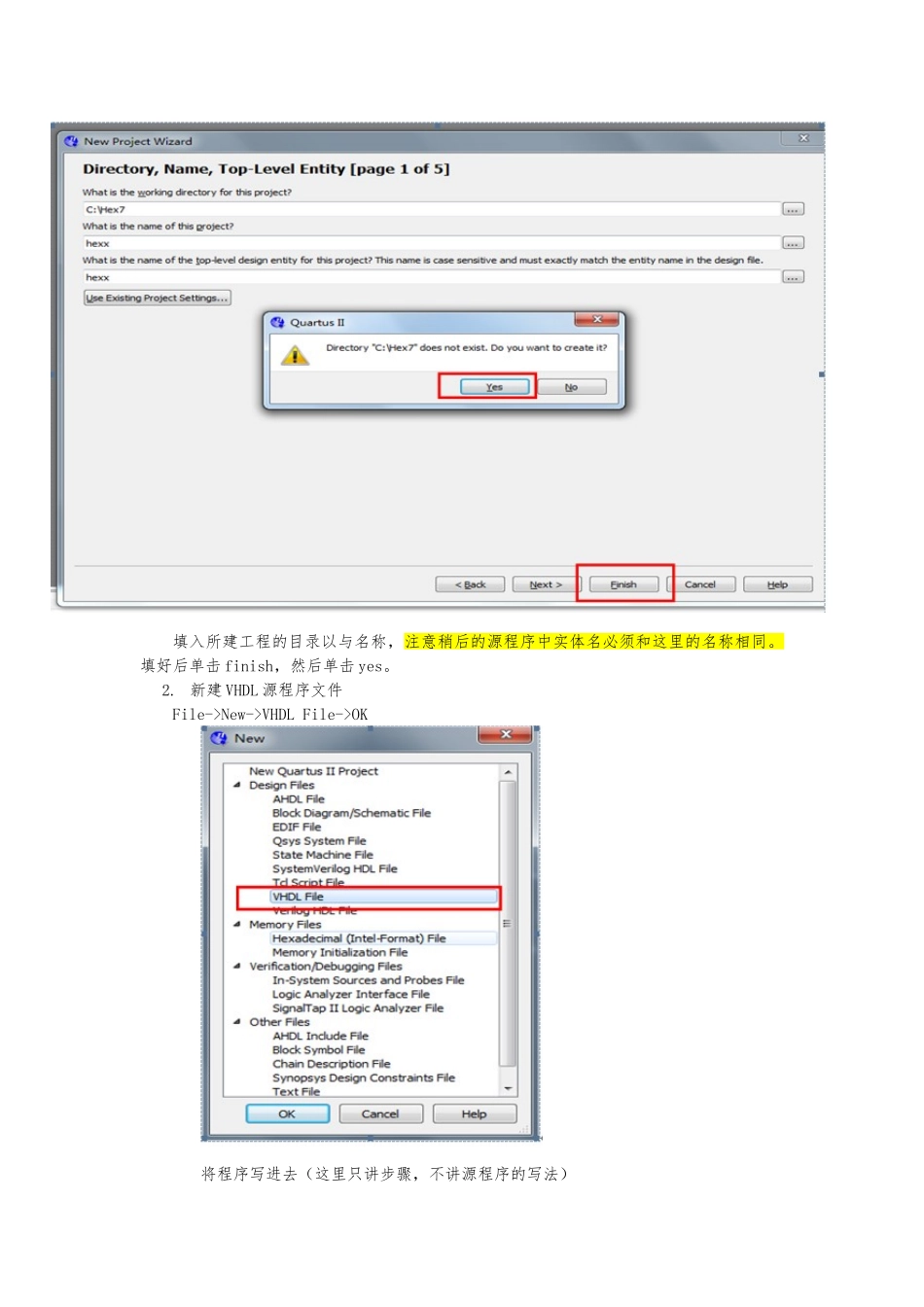

首先建立工程File->New project Wizard(第三个图标)填入所建工程的目录以与名称,注意稍后的源程序中实体名必须和这里的名称相同

填好后单击 finish,然后单击 yes

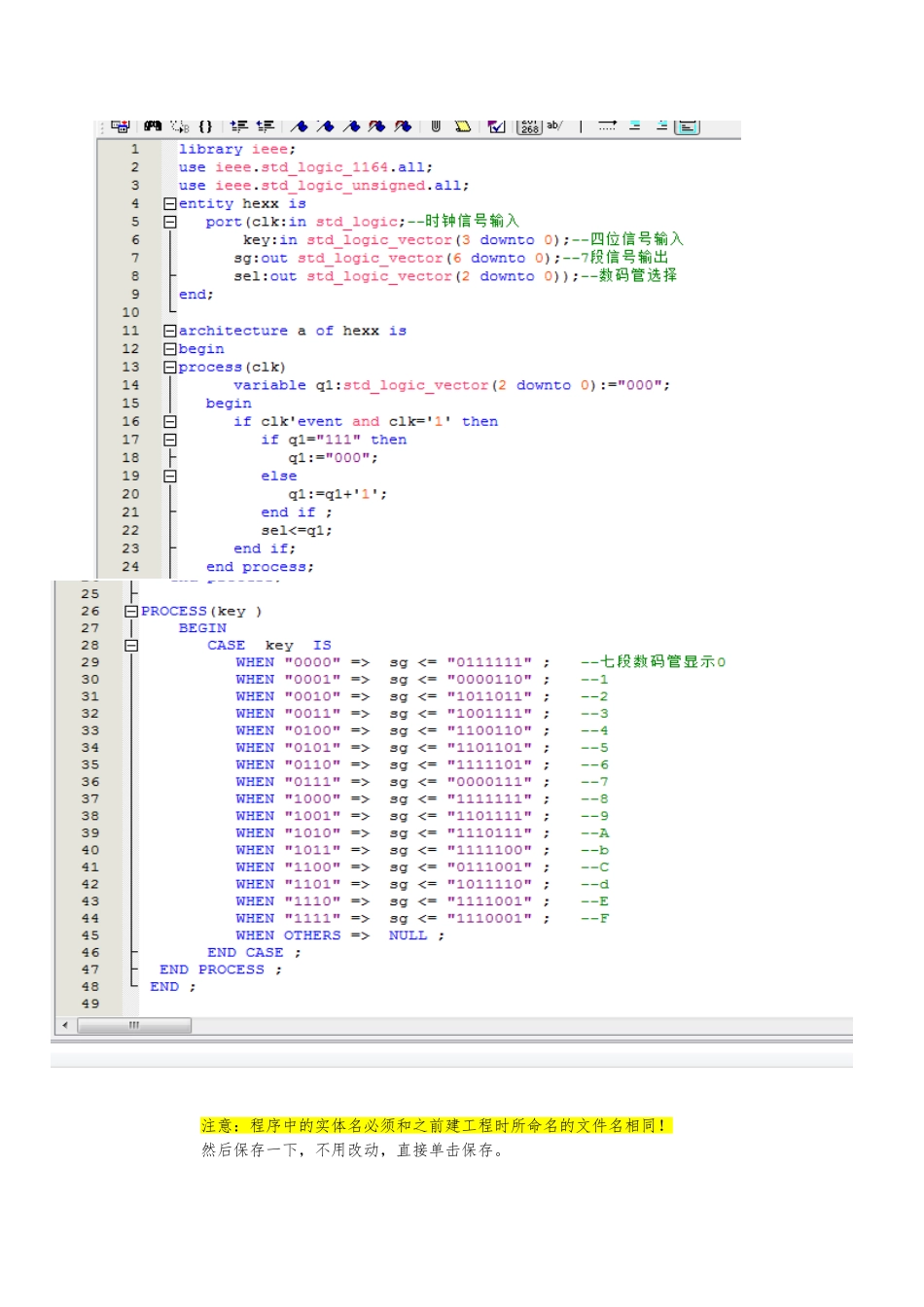

新建 VHDL 源程序文件File->New->VHDL File->OK将程序写进去(这里只讲步骤,不讲源程序的写法)注意:程序中的实体名必须和之前建工程时所命名的文件名相同

然后保存一下,不用改动,直接单击保存

编译快捷键按钮在界面中上方的红色倒三角,显示编译成功之后关闭编译报告

设备设置具体的实验器件根据提供的实验板设定Assignment->Device4

引脚分配 Assignment->Pin Planner在 Location 下的方格中填入对应的硬件引脚,也是根据实验板而定6

引脚分配好之后再次编译一下,使分配的引脚起作用

一、调用 Modelsim1、 设置仿真工具为 Modelsim-alteraTool->Options->EDA Tool Options,在 Modelsim-Altera 后面的地址改为 Modelsim-Altera

exe 在你电脑中的位置,然后点击 OK

2、 写 T