数字时钟设计报告设计目的1. 掌握数字钟的设计、组装与调试方法

2. 熟悉继承电路的使用方法

设计内容要求基本要求:1

设计一个有“时”、“分”、“秒”(23 小时 59 分 59 秒)显示且有校时功能的电子钟

用中小规模集成电路组成电子钟,并在 Multisim 中进行组装、调试

画出框图和逻辑电路图,写出设计、实验总报告

扩展功能:1

闹钟系统(上午 7 点 59 分发出闹时信号,持续时间为 1min)2

在 59 分 51 秒,53 秒,55 秒,57 秒输出 500Hz 音频信号,在 59 分 59 秒输出 1kHz信号,音响持续 1 秒,在 1kHZ 音响结束时刻为整点

实验条件装有 Mutisim8 的电脑数字钟系统设计1

整体框架图译码器译码器译码器2

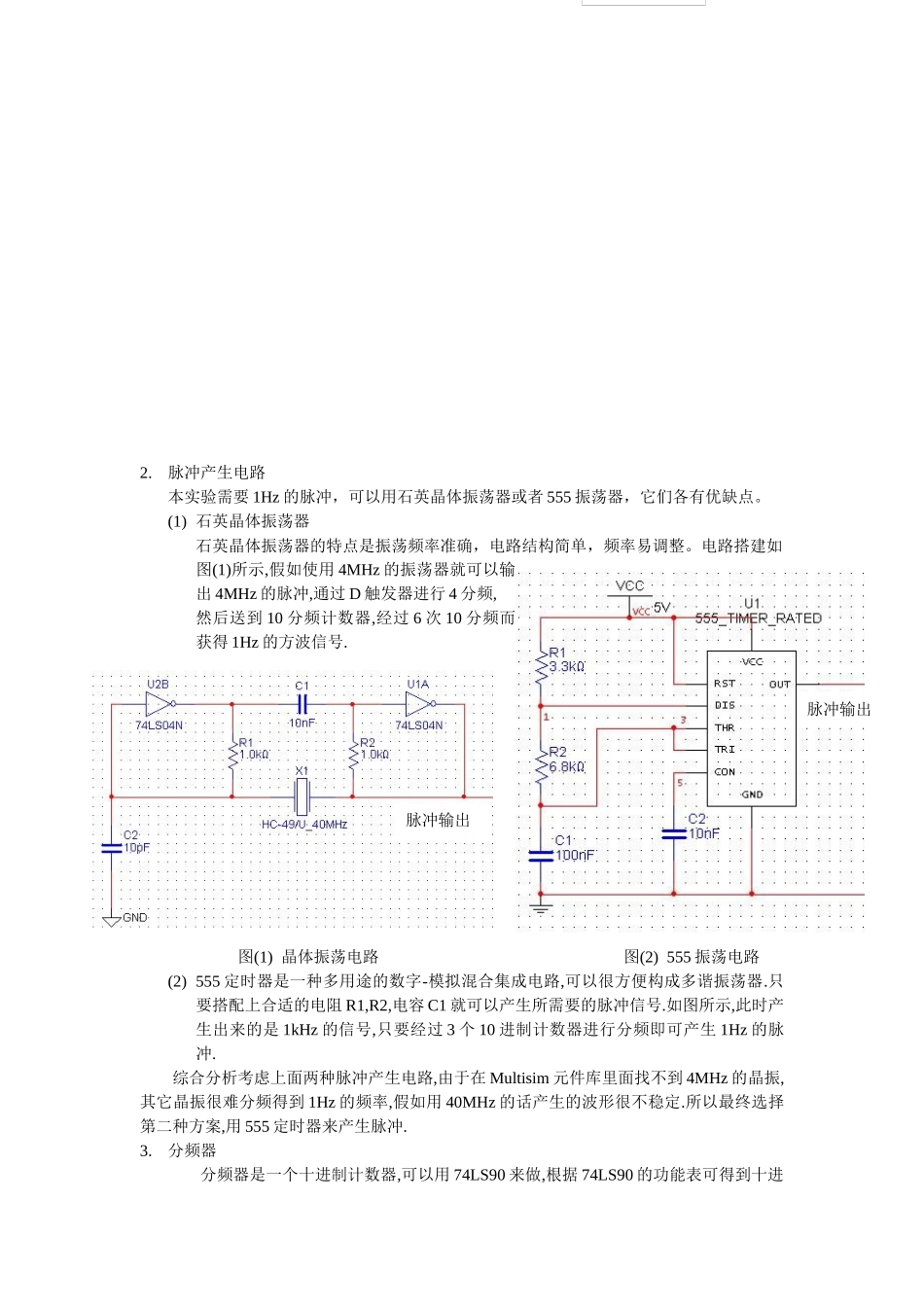

脉冲产生电路本实验需要 1Hz 的脉冲,可以用石英晶体振荡器或者 555 振荡器,它们各有优缺点

(1) 石英晶体振荡器石英晶体振荡器的特点是振荡频率准确,电路结构简单,频率易调整

电路搭建如图(1)所示,假如使用 4MHz 的振荡器就可以输出 4MHz 的脉冲,通过 D 触发器进行 4 分频,然后送到 10 分频计数器,经过 6 次 10 分频而获得 1Hz 的方波信号

图(1) 晶体振荡电路 图(2) 555 振荡电路(2) 555 定时器是一种多用途的数字-模拟混合集成电路,可以很方便构成多谐振荡器

只要搭配上合适的电阻 R1,R2,电容 C1 就可以产生所需要的脉冲信号

如图所示,此时产生出来的是 1kHz 的信号,只要经过 3 个 10 进制计数器进行分频即可产生 1Hz 的脉冲

综合分析考虑上面两种脉冲产生电路,由于在 Multisim 元件库里面找不到 4MHz 的晶振,其它晶振很难分频得到 1Hz 的频率,假如用 40MHz 的话产生的波形很不稳定

所以最终选择第二种方案,用