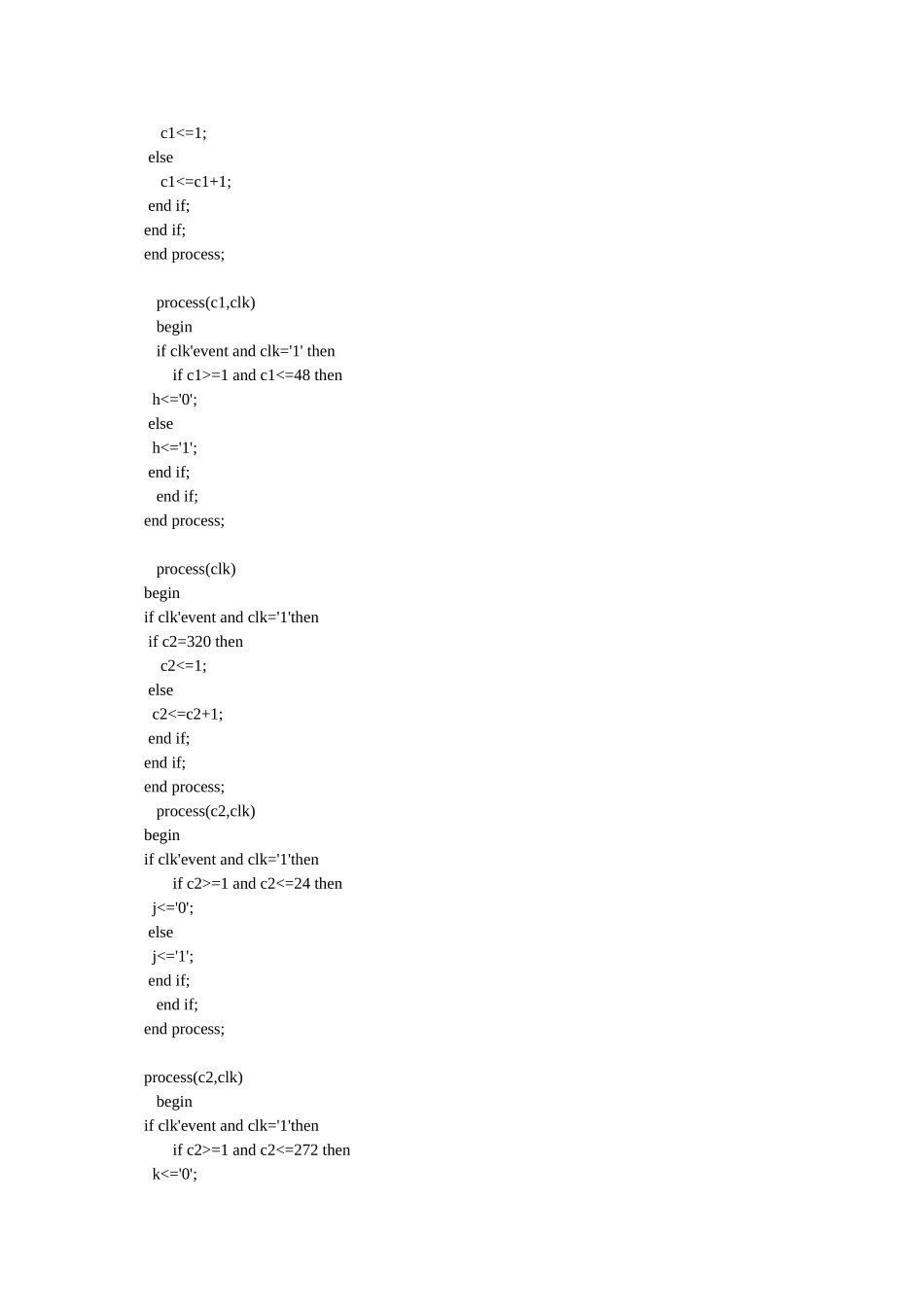

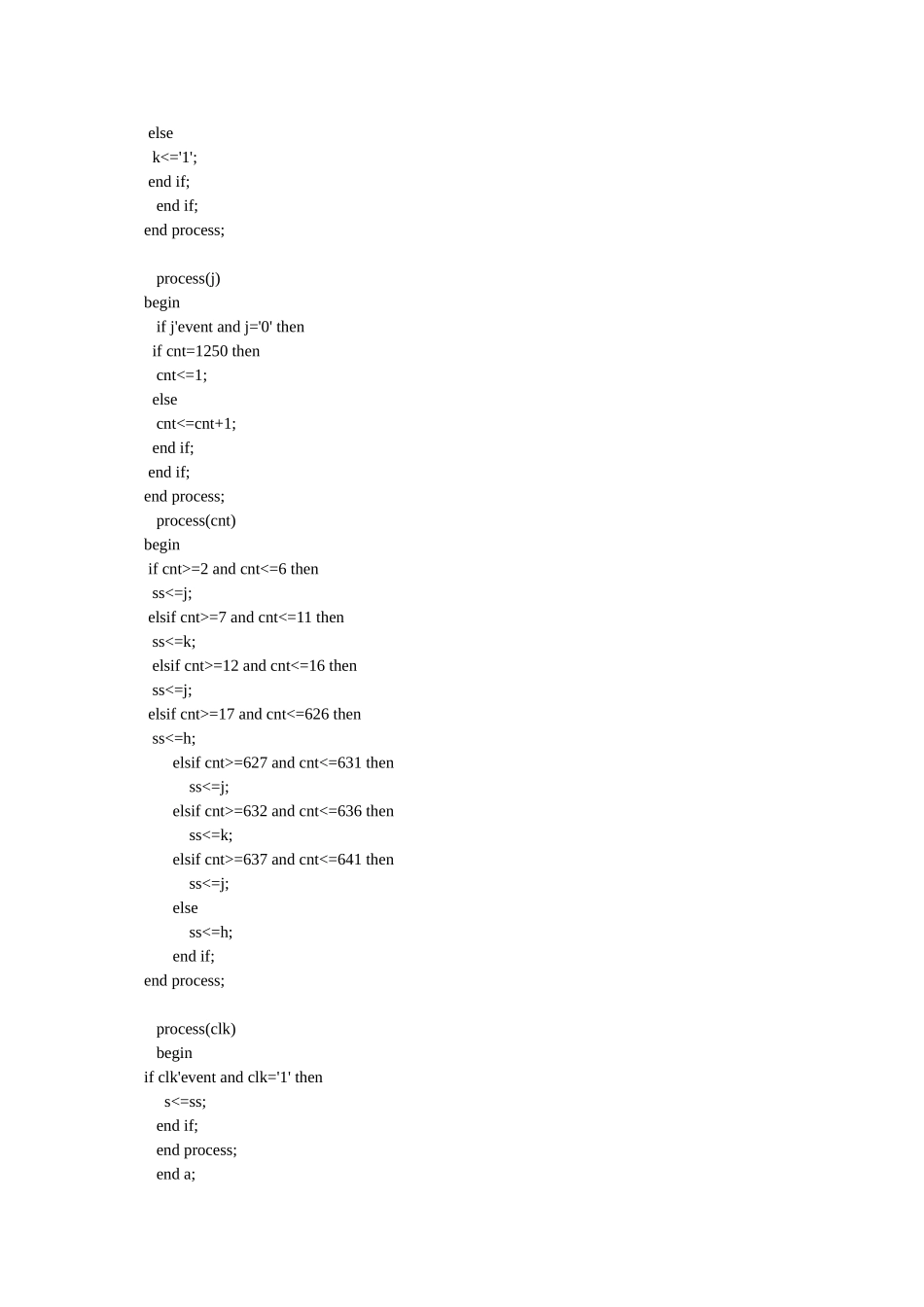

基于VHDL的同步信号产生探讨本文介绍了通过VHDL语言,利用Max-plusⅡ软件设计一个图象同步信号处理电路,产生视频图形信号中的复合同步信号波形,并且从复合同步信号中分拣出行同步、场同步、行消隐、场消隐和奇偶场标志信号。关键词:VHDL视频图像复合同步信号Max-plusⅡ作为一个仿真软件现在已经基本不用了,淘汰了。现在的主流是使用QuartusⅡ。VHDL语言是一种硬件描述语言,而且这种语言极为复杂和正式,很多人会选择使用veriloghdl语言,它相对于VHDL较为接近C语言的风格,所以很容易被接受。但是,只有能学会VHDL,veriloghdl就很容易上手。内容一本实验要求产生的视频图象复合同步信号由奇偶2场(1帧)重复组成,每场312.5行,由均衡脉冲、槽脉冲、行同步信号组成。设计的中心思想是以计数器分别设计出均衡脉冲信号J、开槽脉冲信号K、行同步信号H,然后再合成所需要的复合同步信号。实验中,输入为频率为10M的的时钟脉冲CLK,根据设计需要,定义J、K、H、ss为输入输出信号,并在构造体中设定计数器中的中间变量c1、c2、cnt,s为输出信号。均衡脉冲信号的周期为32μs,脉宽为2.4μs。所以定义c2为320的计数器。以clk为时钟信号,只要c2小于320,每来一个clk的上升沿时c2=c2+1,当c2=320时置c2=1。然后以c2(半行)作为计数周期,在1≤c2≤24时置J为0,否则置J为1。此时均衡信号设计完成。以同样的方法设计出行同步信号和开槽脉冲信号。然后需要将这三组信号复合成需要的信号。具体的做法是以半行为计数周期,设计一个1250的计数器cnt。再以cnt为计数周期,由于奇数场的两个均衡和槽脉冲共占7.5行,为了保证波形的正确性,奇数场的前均衡脉冲从cnt=2开始。到这时,复合同步信号的设计已基本完成。然而波形中存在毛刺。因此在定义H、J、K信号时需要对准clk时钟。当clk上升沿到来时,信号才发生变化。最后当clk上升沿来临时,将输入输出信号ss赋予s信号,s信号就是最终的复合同步信号。具体程序如下:libraryieee;useieee.std_logic_1164.all;entityssisport(clk:instd_logic;h,j,k,ss:inoutstd_logic;s:outstd_logic);endss;architectureaofssissignalc1:integerrange1to640;signalc2:integerrange1to320;signalcnt:integerrange1to1250;beginprocess(clk)beginifclk'eventandclk='1'thenifc1=640thenc1<=1;elsec1<=c1+1;endif;endif;endprocess;process(c1,clk)beginifclk'eventandclk='1'thenifc1>=1andc1<=48thenh<='0';elseh<='1';endif;endif;endprocess;process(clk)beginifclk'eventandclk='1'thenifc2=320thenc2<=1;elsec2<=c2+1;endif;endif;endprocess;process(c2,clk)beginifclk'eventandclk='1'thenifc2>=1andc2<=24thenj<='0';elsej<='1';endif;endif;endprocess;process(c2,clk)beginifclk'eventandclk='1'thenifc2>=1andc2<=272thenk<='0';elsek<='1';endif;endif;endprocess;process(j)beginifj'eventandj='0'thenifcnt=1250thencnt<=1;elsecnt<=cnt+1;endif;endif;endprocess;process(cnt)beginifcnt>=2andcnt<=6thenss<=j;elsifcnt>=7andcnt<=11thenss<=k;elsifcnt>=12andcnt<=16thenss<=j;elsifcnt>=17andcnt<=626thenss<=h;elsifcnt>=627andcnt<=631thenss<=j;elsifcnt>=632andcnt<=636thenss<=k;elsifcnt>=637andcnt<=641thenss<=j;elsess<=h;endif;endprocess;process(clk)beginifclk'eventandclk='1'thens<=ss;endif;endprocess;enda;在本程序中需要注意:在VHDL语言中,大小写都可以的,但是在行业内,一些VHDL专用语一般用大写,用户自己定义的名称等一般用小写。因为这些语句其实可以是商品,可以买钱的。作为商品就有一定的行内规定,要让顾客容易看懂。以上程序仅供参考,且为本人自己编写,互相学习交流之用