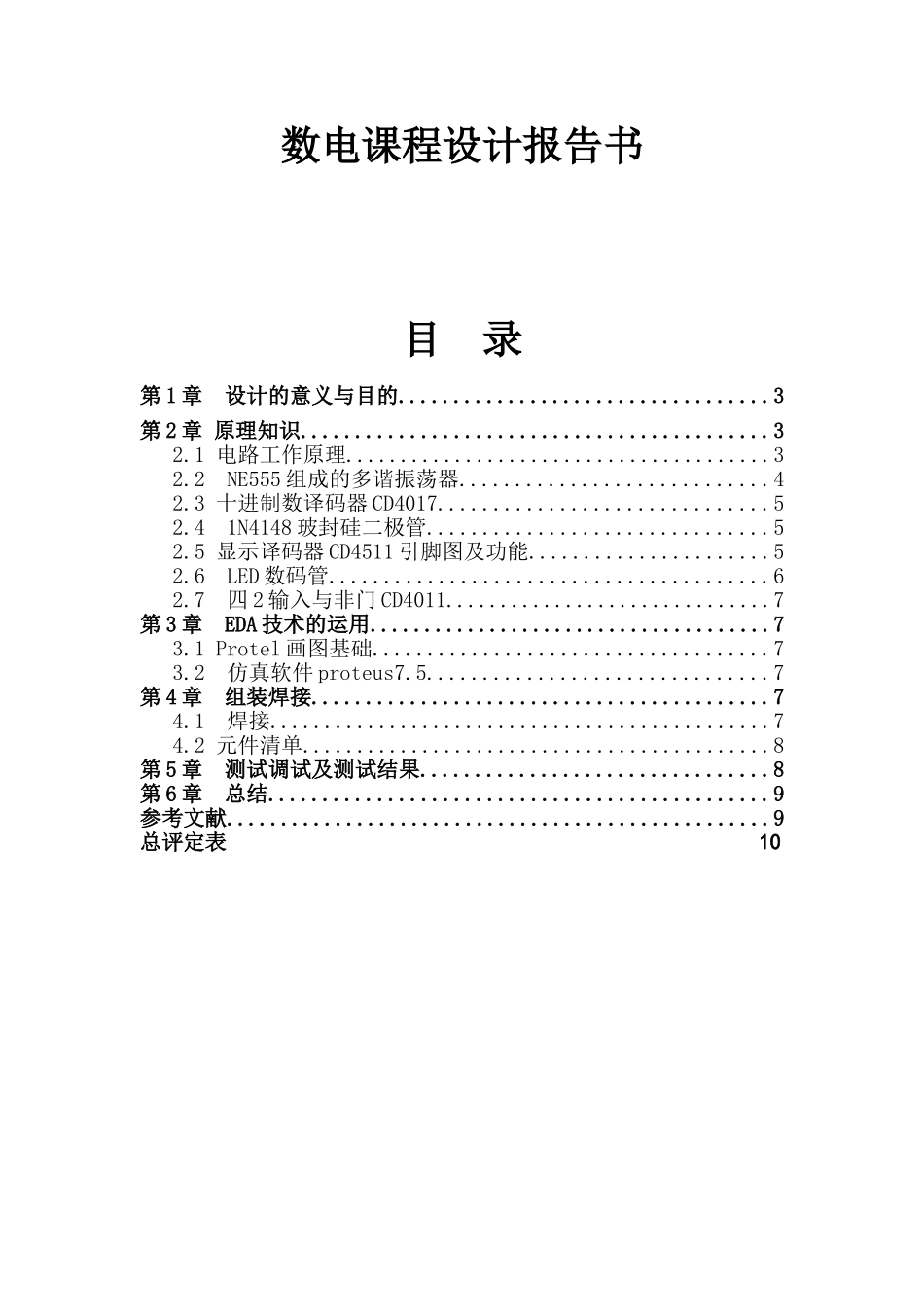

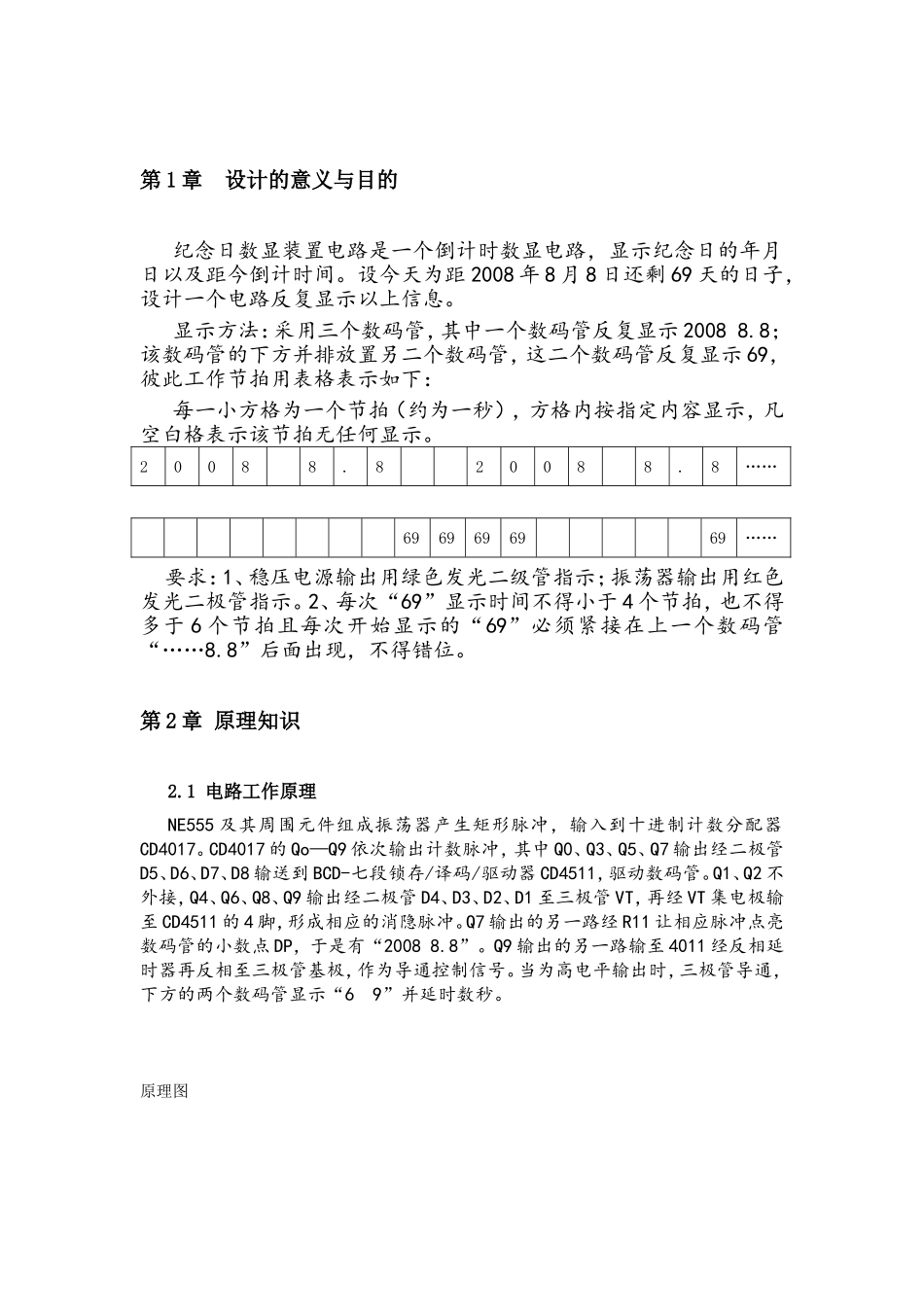

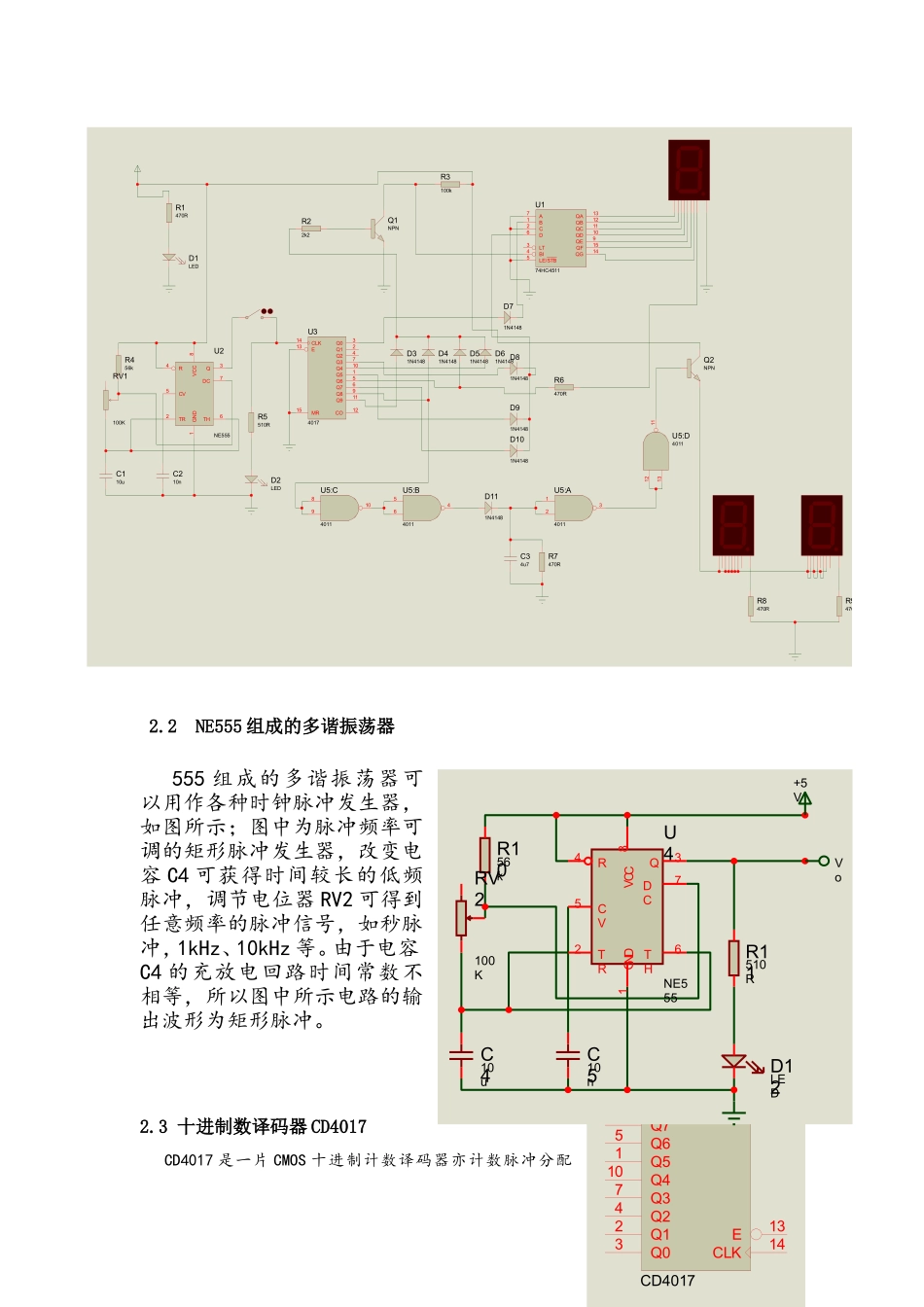

数电课程设计报告书目录第1章设计的意义与目的..................................3第2章原理知识...........................................32.1电路工作原理.......................................32.2NE555组成的多谐振荡器............................42.3十进制数译码器CD4017..............................52.41N4148玻封硅二极管...............................52.5显示译码器CD4511引脚图及功能......................52.6LED数码管........................................62.7四2输入与非门CD4011..............................7第3章EDA技术的运用.....................................73.1Protel画图基础....................................73.2仿真软件proteus7.5...............................7第4章组装焊接..........................................74.1焊接..............................................74.2元件清单...........................................8第5章测试调试及测试结果................................8第6章总结..............................................9参考文献..................................................9总评定表10第1章设计的意义与目的纪念日数显装置电路是一个倒计时数显电路,显示纪念日的年月日以及距今倒计时间。设今天为距2008年8月8日还剩69天的日子,设计一个电路反复显示以上信息。显示方法:采用三个数码管,其中一个数码管反复显示20088.8;该数码管的下方并排放置另二个数码管,这二个数码管反复显示69,彼此工作节拍用表格表示如下:每一小方格为一个节拍(约为一秒),方格内按指定内容显示,凡空白格表示该节拍无任何显示。20088.820088.8……6969696969……要求:1、稳压电源输出用绿色发光二级管指示;振荡器输出用红色发光二极管指示。2、每次“69”显示时间不得小于4个节拍,也不得多于6个节拍且每次开始显示的“69”必须紧接在上一个数码管“……8.8”后面出现,不得错位。第2章原理知识2.1电路工作原理NE555及其周围元件组成振荡器产生矩形脉冲,输入到十进制计数分配器CD4017。CD4017的Qo—Q9依次输出计数脉冲,其中Q0、Q3、Q5、Q7输出经二极管D5、D6、D7、D8输送到BCD-七段锁存/译码/驱动器CD4511,驱动数码管。Q1、Q2不外接,Q4、Q6、Q8、Q9输出经二极管D4、D3、D2、D1至三极管VT,再经VT集电极输至CD4511的4脚,形成相应的消隐脉冲。Q7输出的另一路经R11让相应脉冲点亮数码管的小数点DP,于是有“20088.8”。Q9输出的另一路输至4011经反相延时器再反相至三极管基极,作为导通控制信号。当为高电平输出时,三极管导通,下方的两个数码管显示“69”并延时数秒。原理图CLK14E13MR15CO12Q03Q12Q24Q37Q410Q51Q65Q76Q89Q911CD40172.2NE555组成的多谐振荡器555组成的多谐振荡器可以用作各种时钟脉冲发生器,如图所示;图中为脉冲频率可调的矩形脉冲发生器,改变电容C4可获得时间较长的低频脉冲,调节电位器RV2可得到任意频率的脉冲信号,如秒脉冲,1kHz、10kHz等。由于电容C4的充放电回路时间常数不相等,所以图中所示电路的输出波形为矩形脉冲。2.3十进制数译码器CD4017CD4017是一片CMOS十进制计数译码器亦计数脉冲分配R4DC7Q3GND1VCC8TR2TH6CV5U4NE555R1056kRV2100KC410uC510nR11510RD12LED+5VVoR1470RD1LEDR22k2R3100kQ1NPNA7B1C2D6LT3BI4LE/STB5QA13QB12QC11QD10QE9QF15QG14U174HC4511R4DC7Q3GND1VCC8TR2TH6CV5U2NE555R456kRV1100KC110uC210nR5510RD2LEDD31N4148D41N4148D51N4148D61N4148D71N4148D81N4148D91N4148D101N4148R6470R123U5:A4011564U5:B40118910U5:C4011D111N4148C34u7R7470RR8470RR9470RCLK14E13MR15CO12Q03Q12Q24Q37Q410Q51Q65Q76Q89Q911U34017121311U5:D4011Q2NPN器,逻辑功能图如图中所示。共有三个输入端,复位清零端MR,当在MR端输入高电平或正脉冲时,计数器清零,所有输出中只有对应“0”状态时Q0端输出高电平,其余输出均为低电平;CLK、E端为时钟输入端,其中CLK用于上升沿计数,E端用于下降沿计数,彼此间有互锁关系,若利用CLK计数时,E端应接地(低...