数字电路与逻辑设计实验报告实验七 计数器得设计姓名:黄文轩学号:班级:光电一班一、实验目得熟悉 J-K 触发器得逻辑功能,掌握 J-K 触发器构成异步计数器与同步计数器

二、实验器件ﻫ1、数字电路实验箱、数字万用表、示波器

2、虚拟器件: 74 L S73, 74 L S00, 74LS08, 7 4 L S20三、实验预习ﻫ1、 复习时序逻辑电路设计方法①根据设计要求获得真值表②画出卡诺图或使用其她方式确定状态转换得规律③求出各触发器得驱动方程④根据已有方程画出电路图

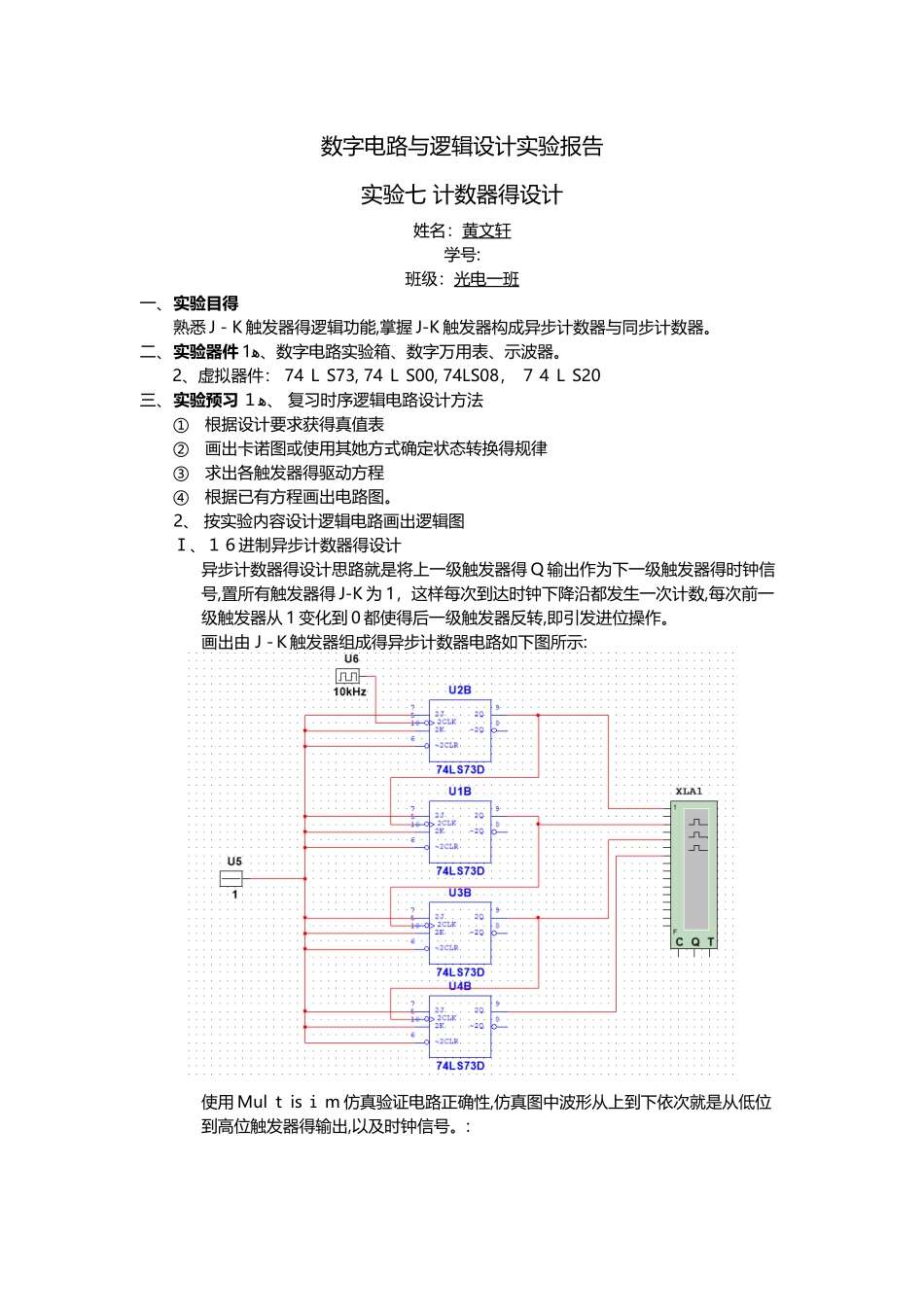

2、 按实验内容设计逻辑电路画出逻辑图Ⅰ、16进制异步计数器得设计异步计数器得设计思路就是将上一级触发器得 Q 输出作为下一级触发器得时钟信号,置所有触发器得 J-K 为 1,这样每次到达时钟下降沿都发生一次计数,每次前一级触发器从 1 变化到 0 都使得后一级触发器反转,即引发进位操作

画出由J-K触发器组成得异步计数器电路如下图所示:使用 Mul t is i m 仿真验证电路正确性,仿真图中波形从上到下依次就是从低位到高位触发器得输出,以及时钟信号

:可以瞧出电路正常执行1 6 进制计数器得功能

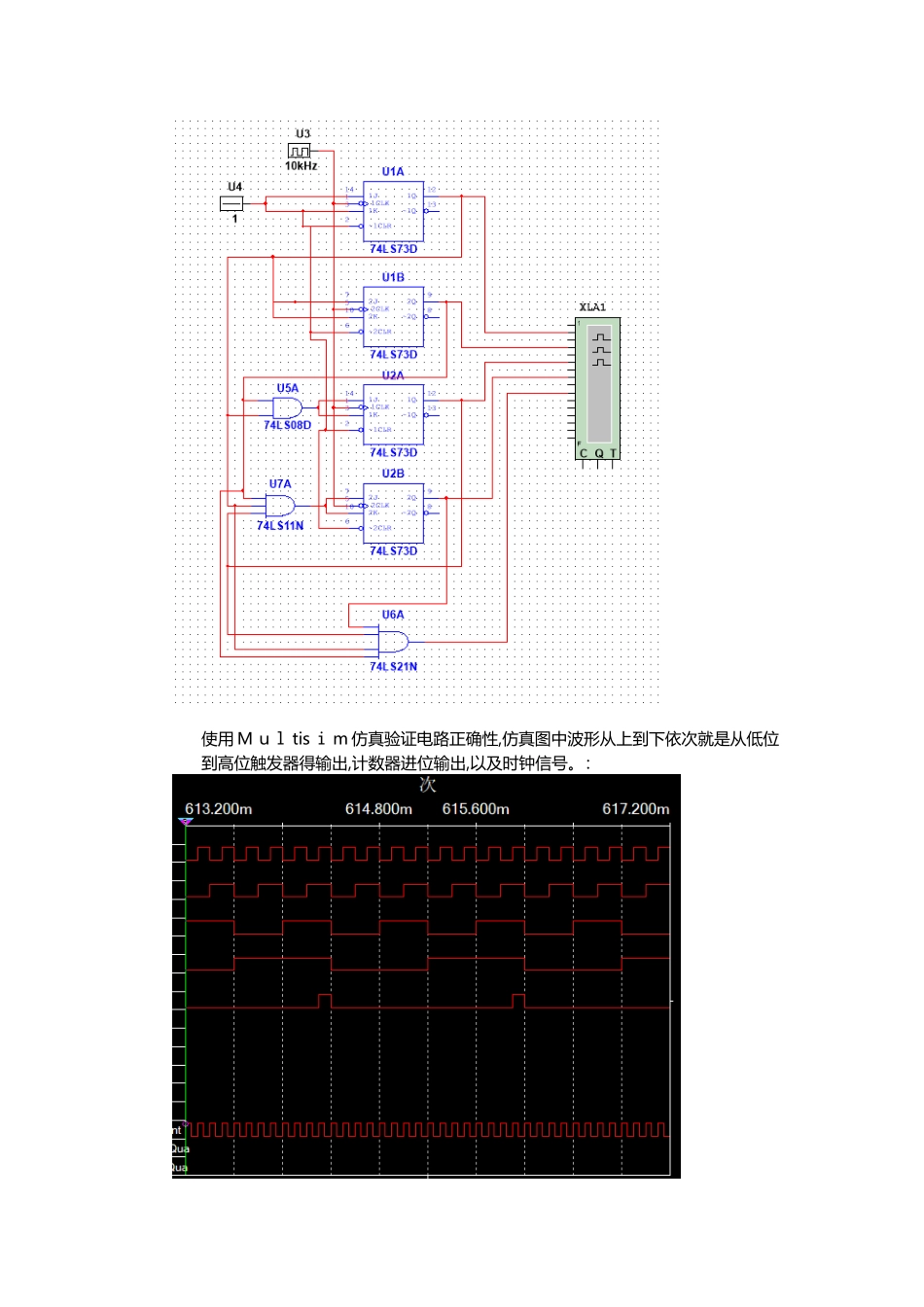

Ⅱ、16 进制同步计数器得设计ﻩ较异步计数器而言,同步计数器要求电路得每一位信号得变化都发生在相同得时间点

因此同步计数器各触发器得时钟脉冲必须就是同一个时钟信号,这样进位信息就要放置在J-K 输入端,我们可以把 J-K 端口接在一起,当时钟下降沿到来时,假如满足进位条件(前几位触发器输出都为 1)则使J K 为 1,发生反转实现进位

画出由 J-K触发器与门电路组成得同步计数器电路如下图所示使用 M ul tis i m 仿真验证电路正确性,仿真图中波形从上到下依次就是从低位到高位触发器得输出,计数器进位输出,以及时钟信号

:可以瞧出电路正常执行 16 进制计数器得功能,且每到 15 就输出进位信号,我们可