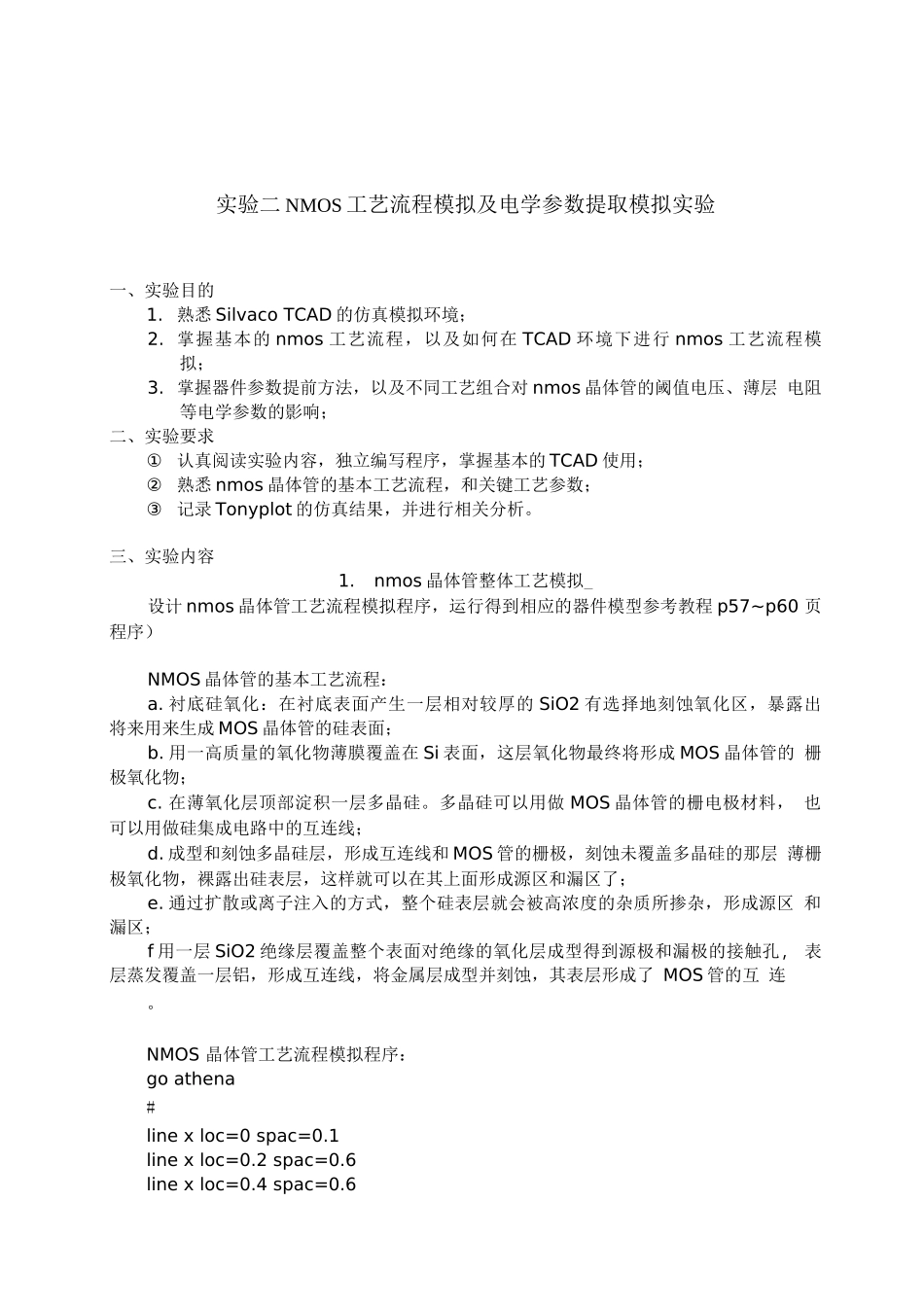

实验二 NMOS 工艺流程模拟及电学参数提取模拟实验一、实验目的1

熟悉 Silvaco TCAD 的仿真模拟环境;2

掌握基本的 nmos 工艺流程,以及如何在 TCAD 环境下进行 nmos 工艺流程模 拟;3

掌握器件参数提前方法,以及不同工艺组合对 nmos 晶体管的阈值电压、薄层 电阻等电学参数的影响;二、实验要求①认真阅读实验内容,独立编写程序,掌握基本的 TCAD 使用;②熟悉 nmos 晶体管的基本工艺流程,和关键工艺参数;③记录 Tonyplot 的仿真结果,并进行相关分析

三、实验内容1

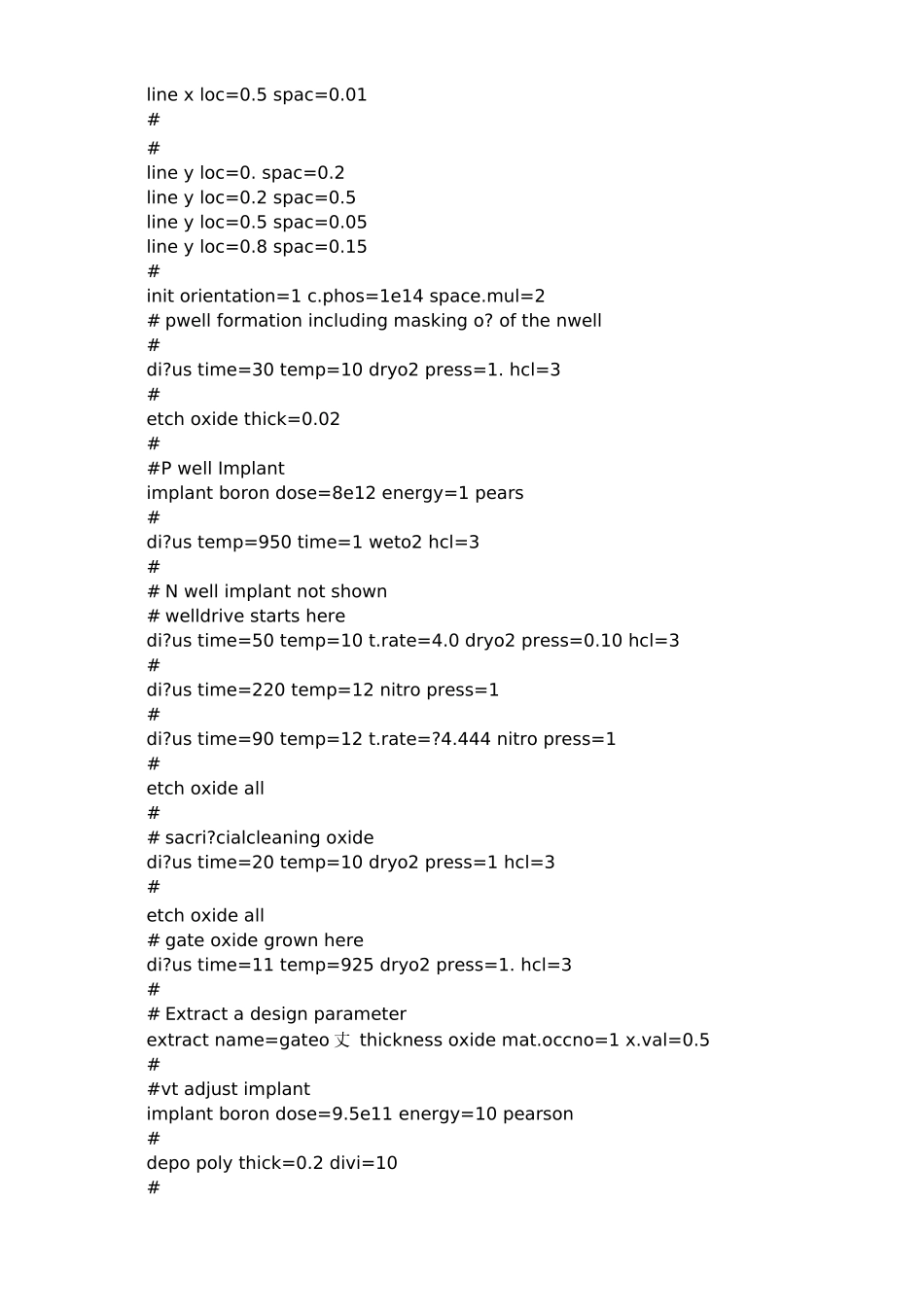

nmos 晶体管整体工艺模拟_设计 nmos 晶体管工艺流程模拟程序,运行得到相应的器件模型参考教程 p57~p60 页程序)NMOS 晶体管的基本工艺流程:a

衬底硅氧化:在衬底表面产生一层相对较厚的 SiO2 有选择地刻蚀氧化区,暴露出 将来用来生成 MOS 晶体管的硅表面;b

用一高质量的氧化物薄膜覆盖在 Si 表面,这层氧化物最终将形成 MOS 晶体管的 栅极氧化物;c

在薄氧化层顶部淀积一层多晶硅

多晶硅可以用做 MOS 晶体管的栅电极材料, 也可以用做硅集成电路中的互连线;d

成型和刻蚀多晶硅层,形成互连线和 MOS 管的栅极,刻蚀未覆盖多晶硅的那层 薄栅极氧化物,裸露出硅表层,这样就可以在其上面形成源区和漏区了;e

通过扩散或离子注入的方式,整个硅表层就会被高浓度的杂质所掺杂,形成源区 和漏区;f 用一层 SiO2 绝缘层覆盖整个表面对绝缘的氧化层成型得到源极和漏极的接触孔 , 表层蒸发覆盖一层铝,形成互连线,将金属层成型并刻蚀,其表层形成了 MOS 管的互 连

NMOS 晶体管工艺流程模拟程序:go athena#line x loc=0 spac=0

1line x loc=0

2 spac=0

6line x loc=0

4 spac