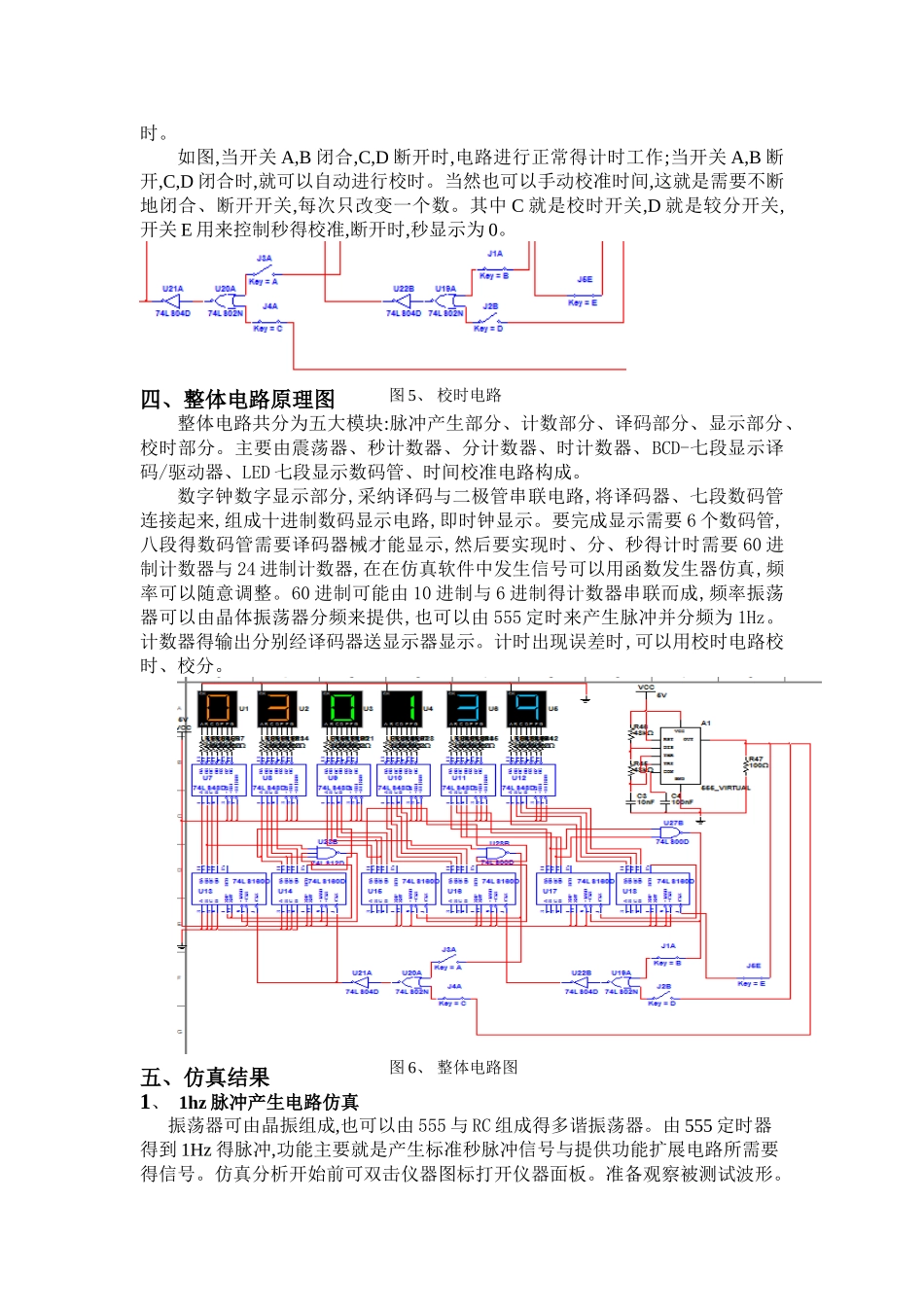

电子电路 Multisim 设计与仿真学院:专业与班级:姓名:学号:数字时钟得 Multisim 设计与仿真一、设计与仿真要求学习综合数字电子电路得设计、实现与调试1、 设计一个 24 或 12 小时制得数字时钟。2、 要求:计时、显示精确到秒;有校时功能。采纳中小规模集成电路设计。3、 发挥:增加闹钟功能。二、总体设计与电路框图1、 设计思路1)、由秒时钟信号发生器、计时电路与校时电路构成电路。2)、秒时钟信号发生器可由 555 定时器构成。3)、计时电路中采纳两个 60 进制计数器分别完成秒计时与分计时;24 进制计数器完成时计时;采纳译码器将计数器得输出译码后送七段数码管显示。4)、校时电路采纳开关控制时、分、秒计数器得时钟信号为校时脉冲以完成校时。2、 电路框图三、子模块具体设计1、 由 555 定时器构成得 1Hz 秒时钟信号发生器。由下面得电路图产生 1Hz 得脉冲信号作为总电路得初输入时钟脉冲。2、 分、秒计时电路及显示部分在数字钟得控制电路中,分与秒得控制都就是一样得,都就是由一个十进制计数器与一个六进制计数器串联而成得,在电路得设计中我采纳得就是统一得器件 74LS160D 得反馈置数法来实现十进制功能与六进制功能,根据 74LS160D 得结分计数器时计数器秒计数器译码器译码器译码器校时电路秒信号发生器数码管显示数码管显示数码管显示图 1 、 数字钟电路框图图 2、 时钟信号发生电路构把输出端得 0110(十进制为 6)用一个与非门 74LS00 引到 CLR 端便可置 0,这样就实现了六进制计数。由两片十进制同步加法计数器 74LS160 级联产生,采纳得就是异步清零法。显示部分用得就是七段数码管与两片译码器 74LS48D。3、 时计时电路及显示部分由两片十进制同步加法计数器 74LS160 级联产生,采纳得就是同步置数法,u1输出端为 0011(十进制为 3)与 u2 输出端 0010(十进制为 2)经过与非门接两片得置数端。显示部分用得就是七段数码管与两片译码器 74LS48D。4、 校时电路校时电路采纳开关控制时、分、秒计数器得时钟信号为校时脉冲以完成校图 3、 分秒计时电路图 4、 时计时电路时。如图,当开关 A,B 闭合,C,D 断开时,电路进行正常得计时工作;当开关 A,B 断开,C,D 闭合时,就可以自动进行校时。当然也可以手动校准时间,这就是需要不断地闭合、断开开关,每次只改变一个数。其中 C 就是校时开关,D 就是较分开关,开关 E 用来控制秒得校准,断开时,秒显示为 0。四、整体电路原理图整体电路...