数字电路实验报告实验一 组合逻辑电路分析一

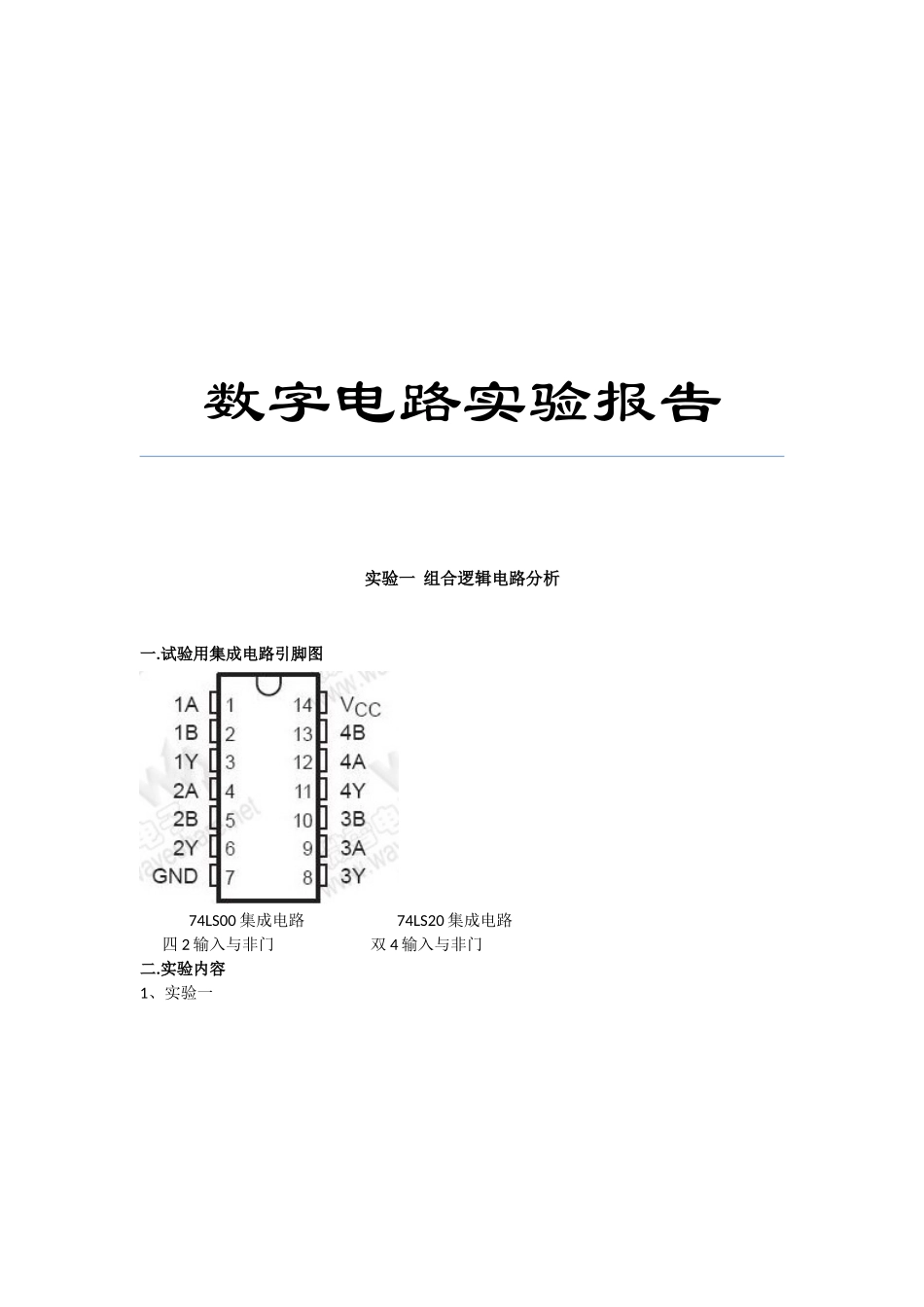

试验用集成电路引脚图 74LS00 集成电路 74LS20 集成电路 四 2 输入与非门 双 4 输入与非门二

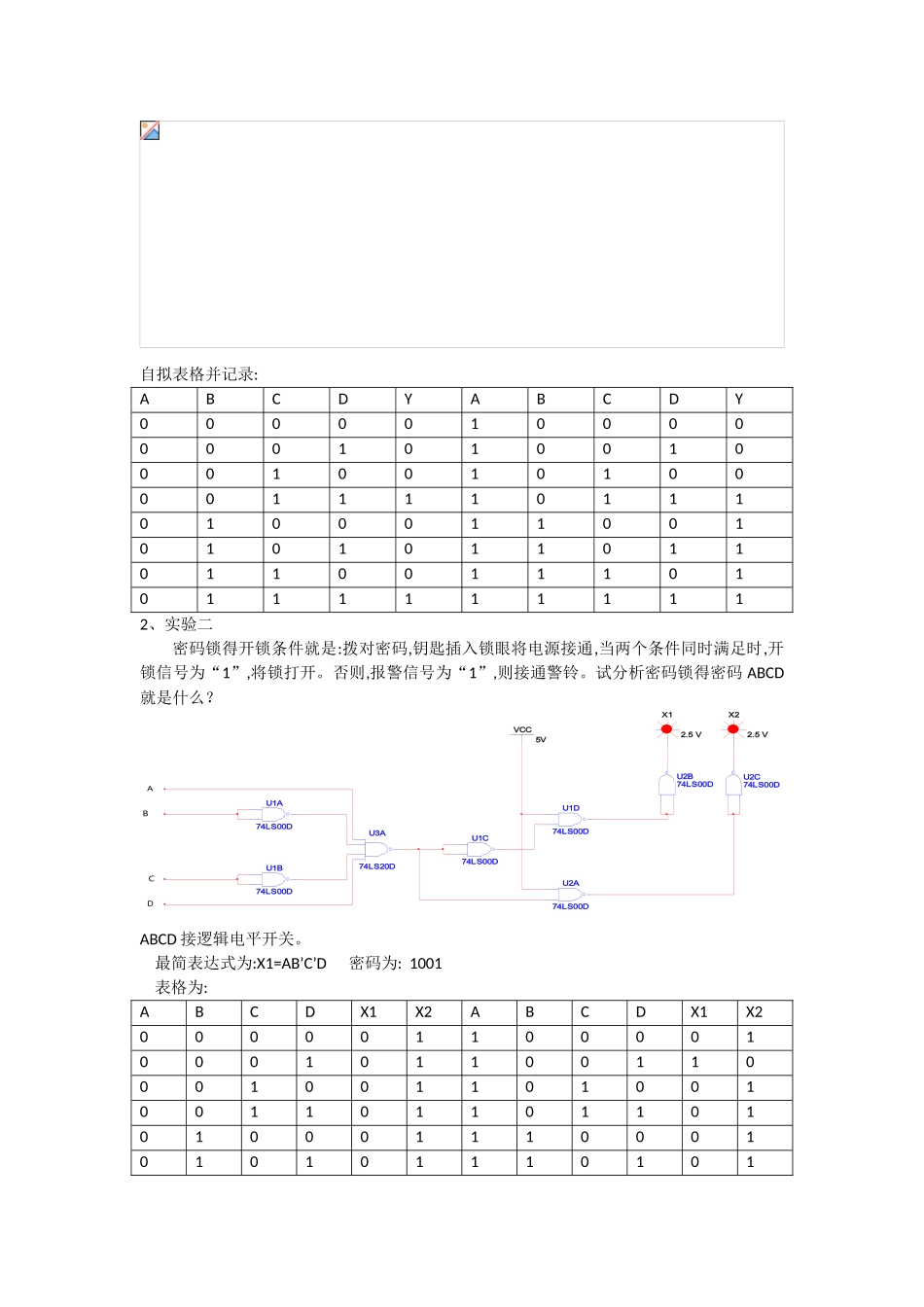

实验内容1、实验一自拟表格并记录:ABCDYABCDY000001000000010100100010010100001111011101000110010101011011011001110101111111112、实验二密码锁得开锁条件就是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开

否则,报警信号为“1”,则接通警铃

试分析密码锁得密码 ABCD就是什么

U1A74LS00DU1B74LS00DU1C74LS00DU1D74LS00DU2A74LS00DU2B74LS00DU2C74LS00DU3A74LS20DX12

5 V X22

5 V VCC5VABCD ABCD 接逻辑电平开关

最简表达式为:X1=AB’C’D 密码为: 1001 表格为:ABCDX1X2ABCDX1X2000001100001000101100110001001101001001101101101010001110001010101110101011001111001011101111101三、实验体会:1、分析组合逻辑电路时,可以通过逻辑表达式,电路图与真值表之间得相互转换来到达实验所要求得目得

2、这次试验比较简单,熟悉了一些简单得组合逻辑电路与芯片 ,与使用仿真软件来设计与构造逻辑电路来求解

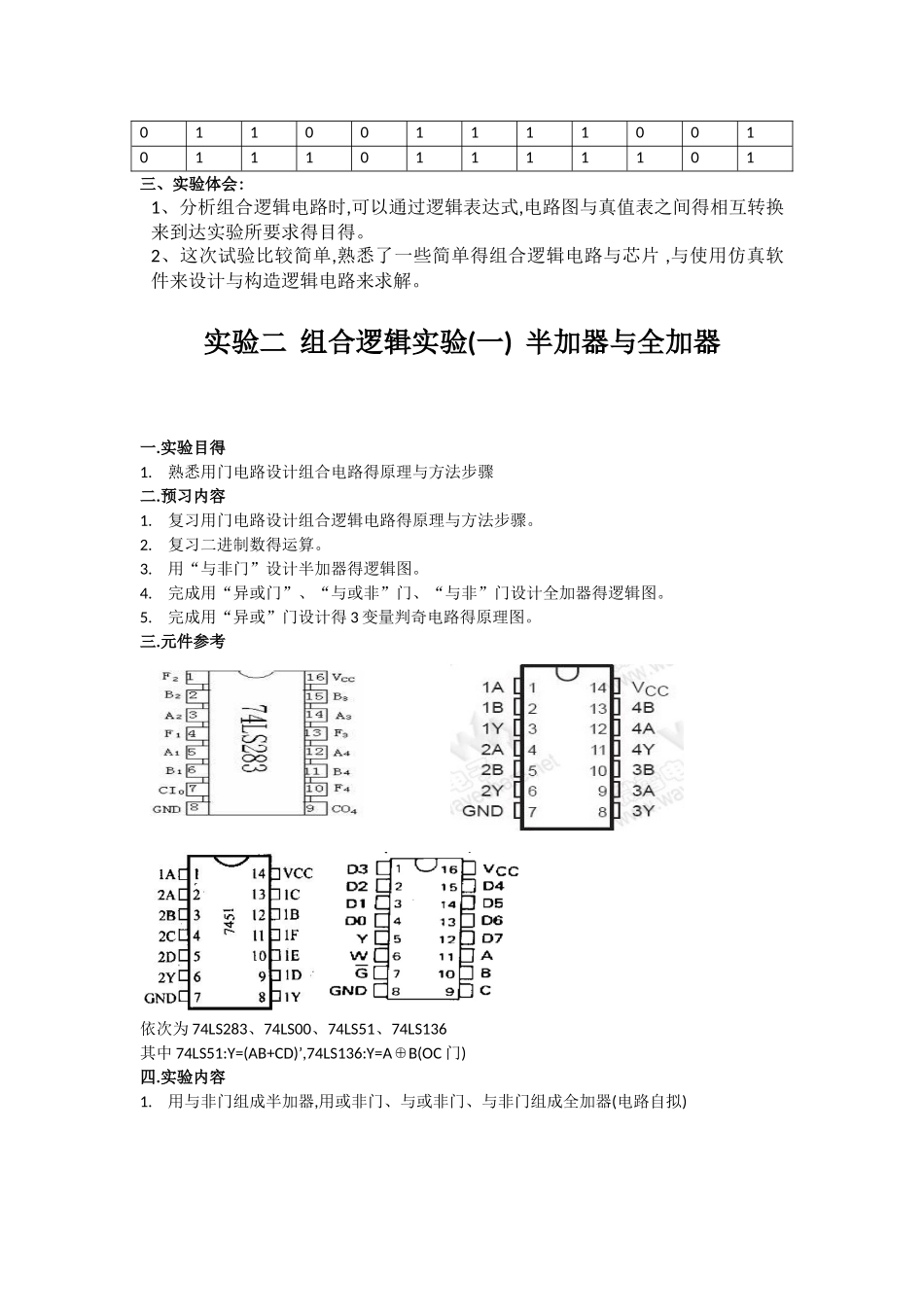

实验二 组合逻辑实验(一) 半加器与全加器一

熟悉用门电路设计组合电路得原理与方法步骤二

复习用门电路设计组合逻辑电路得原理与方法步骤

复习二进制数得运算

用“与非门”设计半加器得逻辑图

完成用“异或门”、“与或非”门、“与非”门设计全加器得逻辑图

完成用“异或