ASIC 流程与工具(1)ASIC 流程(En)Some notes:1

Definition of front-end2

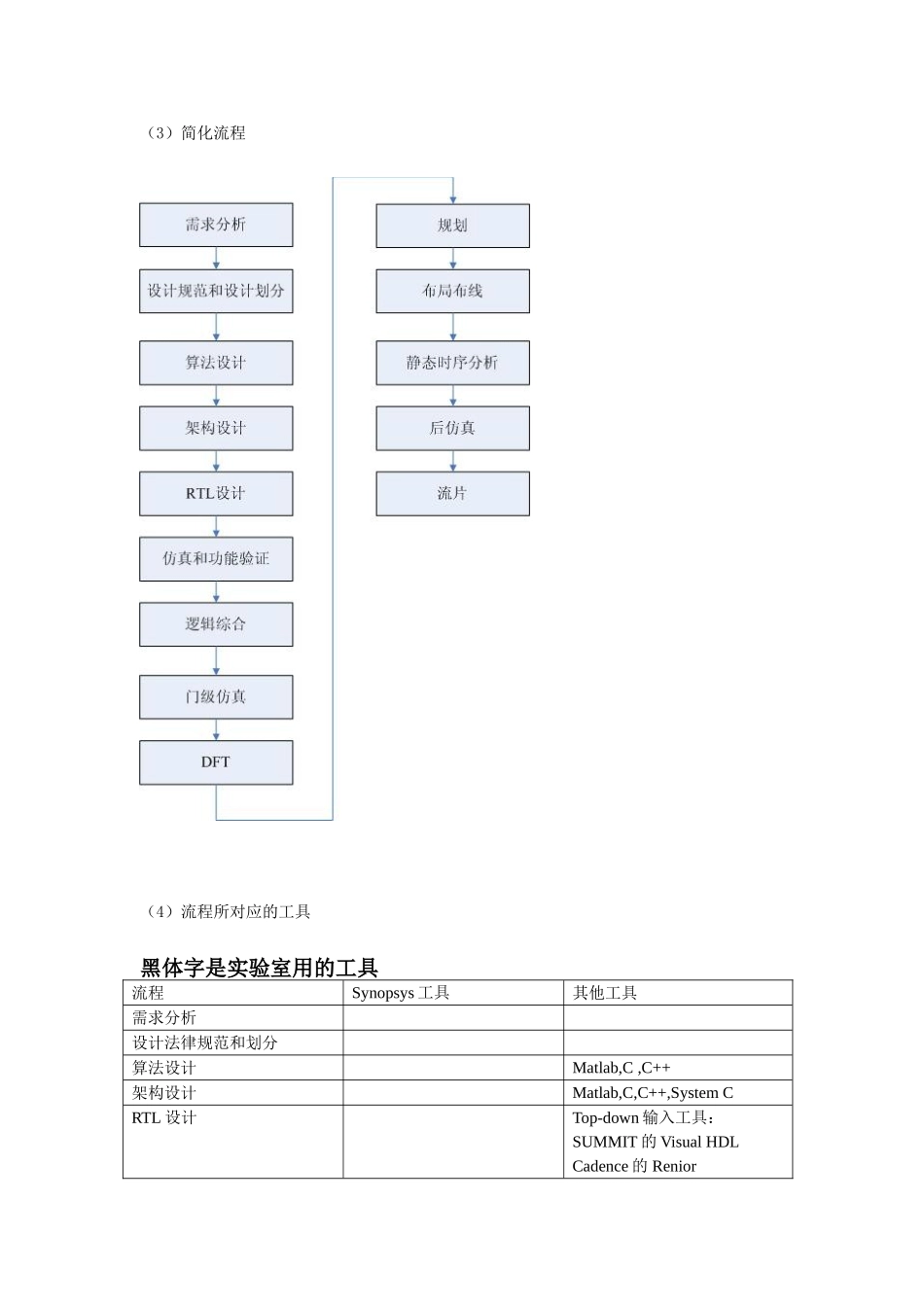

Lack of FPGA prototype(3)简化流程(4)流程所对应的工具黑体字是实验室用的工具 流程Synopsys 工具其他工具需求分析设计法律规范和划分算法设计Matlab,C ,C++ 架构设计Matlab,C,C++,System C RTL 设计Top-down 输入工具:SUMMIT 的 Visual HDLCadence 的 Renior电路图输入工具:Cadence 的 ComposerViewLogic 的 Viewdraw仿真和验证Leda-语法检查VCS-Verilog 仿真Scirocco-VHDL 仿真Vera-验证Cadence NC-VerilogVerilog-XLNCSimMentor ModelSim设计整合与验证Saber-模拟数字混合仿真逻辑综合Design CompilerCadence BuildGates静态时序分析PrimeTime门级仿真VCS可测性设计DFT Compilerdftadvisor规划AstroEncounter,Blast-Fusion, Voltage-storm or redhawk布局Physical CompilerEncounter, Blast-Fusion时钟树综合Astro布线AstroEncounter, Blast-Fusion物理验证HerculesCalibre(Mentor)提取寄生参数Star-RCXT静态时序分析PrimeTime后仿真VCS流片封装测试等效性检查FormalityQuestions:Before tape-out,which routine check should be performed for your layout d