锁相环电路的应用设计与制作一、目的通过对锁相环电路应用设计,进一步加深对锁相环电路工作原理的理解,熟悉锁相环电路的基本形式,掌握集成锁相环电路的测试及应用方法;了解锁相环的相位捕捉的特性检测方法;熟悉单片锁相环集成电路和外围分频集成电路的基本电路应用形式;掌握电路的调整及测量方法;掌握锁相环电路的主要指标参数,为今后的实际工程应用,奠定坚实的基础

二、要求锁相环(PLL)电路是一种反馈控制电路

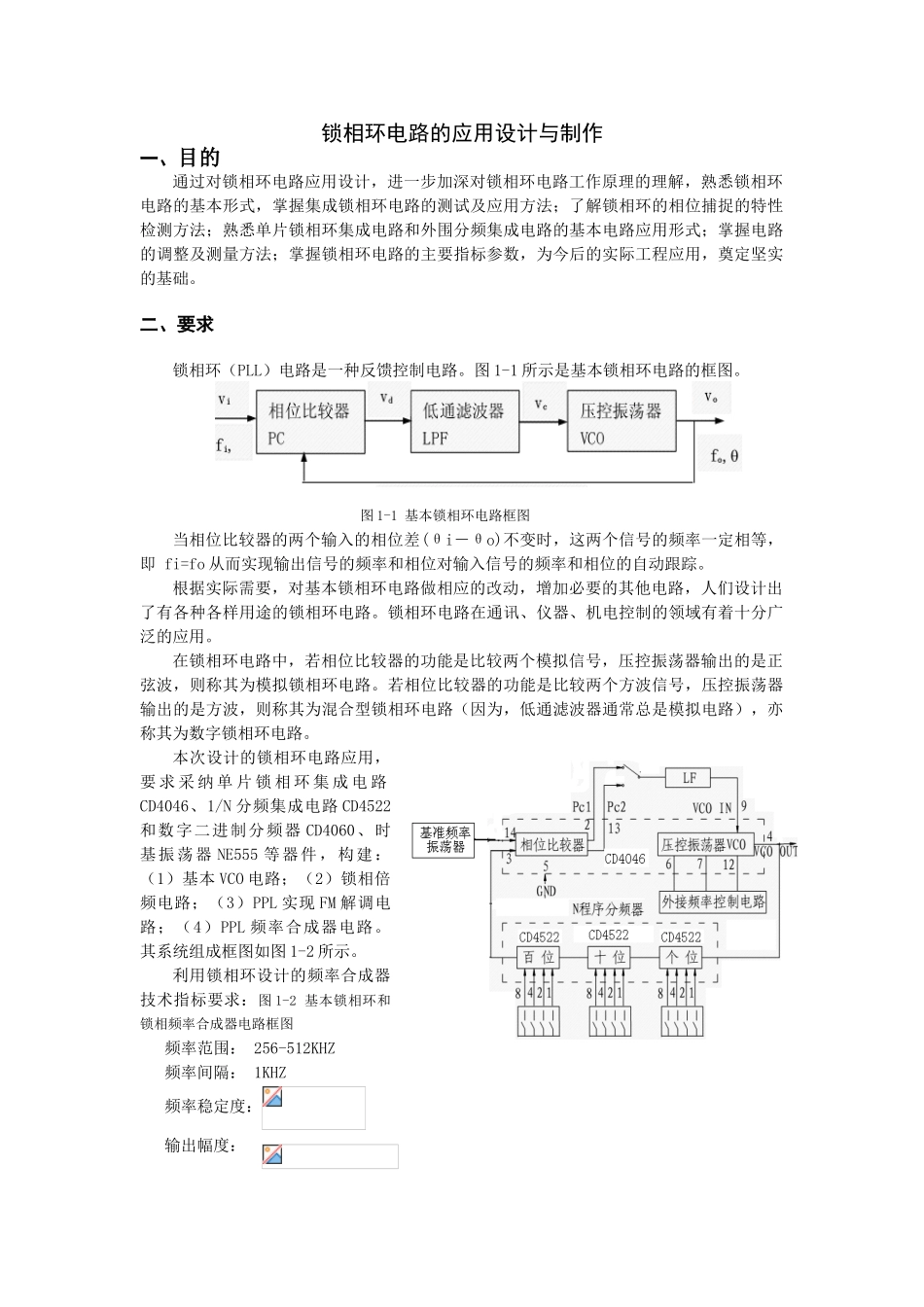

图 1-1 所示是基本锁相环电路的框图

图 1-1 基本锁相环电路框图当相位比较器的两个输入的相位差(θi-θo)不变时,这两个信号的频率一定相等,即 fi=fo 从而实现输出信号的频率和相位对输入信号的频率和相位的自动跟踪

根据实际需要,对基本锁相环电路做相应的改动,增加必要的其他电路,人们设计出了有各种各样用途的锁相环电路

锁相环电路在通讯、仪器、机电控制的领域有着十分广泛的应用

在锁相环电路中,若相位比较器的功能是比较两个模拟信号,压控振荡器输出的是正弦波,则称其为模拟锁相环电路

若相位比较器的功能是比较两个方波信号,压控振荡器输出的是方波,则称其为混合型锁相环电路(因为,低通滤波器通常总是模拟电路),亦称其为数字锁相环电路

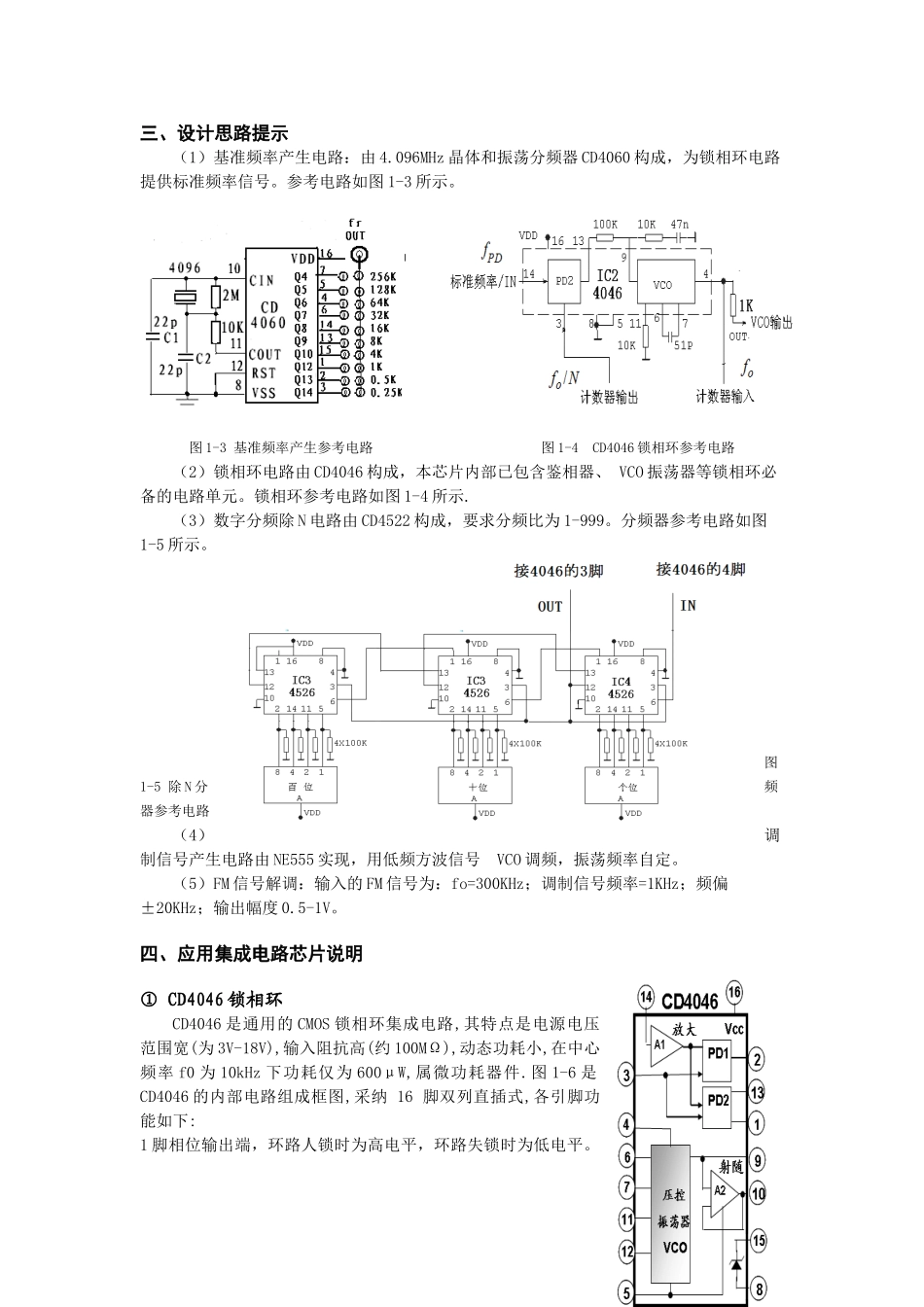

本次设计的锁相环电路应用,要 求 采 纳 单 片 锁 相 环 集 成 电 路CD4046、1/N 分频集成电路 CD4522和数字二进制分频器 CD4060、时基振荡器 NE555 等器件,构建:(1)基本 VCO 电路;(2)锁相倍频电路;(3)PPL 实现 FM 解调电路;(4)PPL 频率合成器电路

其系统组成框图如图 1-2 所示

利用锁相环设计的频率合成器技术指标要求:图 1-2 基本锁相环和锁相频率合成器电路框图频率范围: 256-512KHZ频率间隔: 1KHZ频率稳定度: 输出幅度: 三、设计思路提示(1)基准频率产生电路:由 4