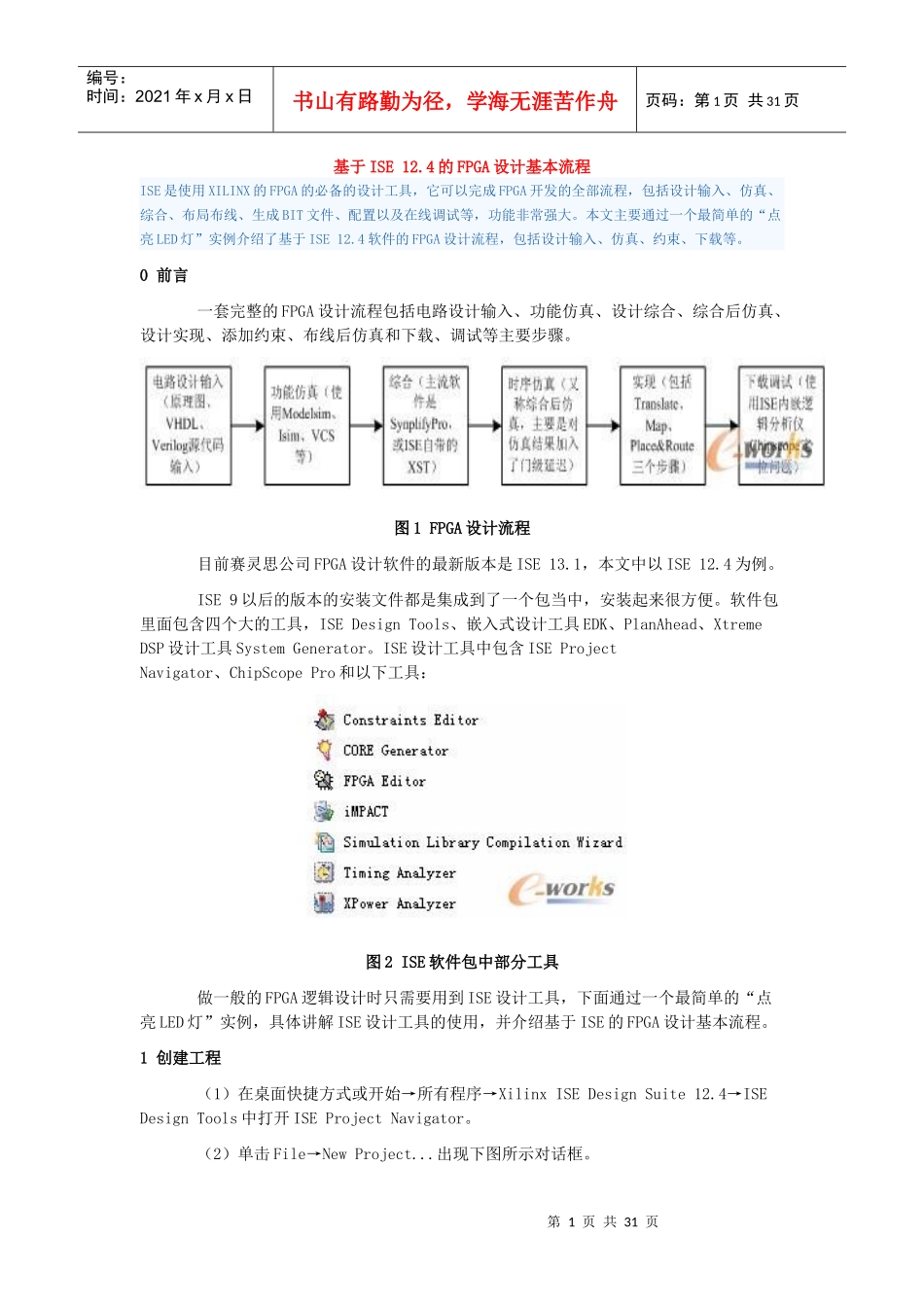

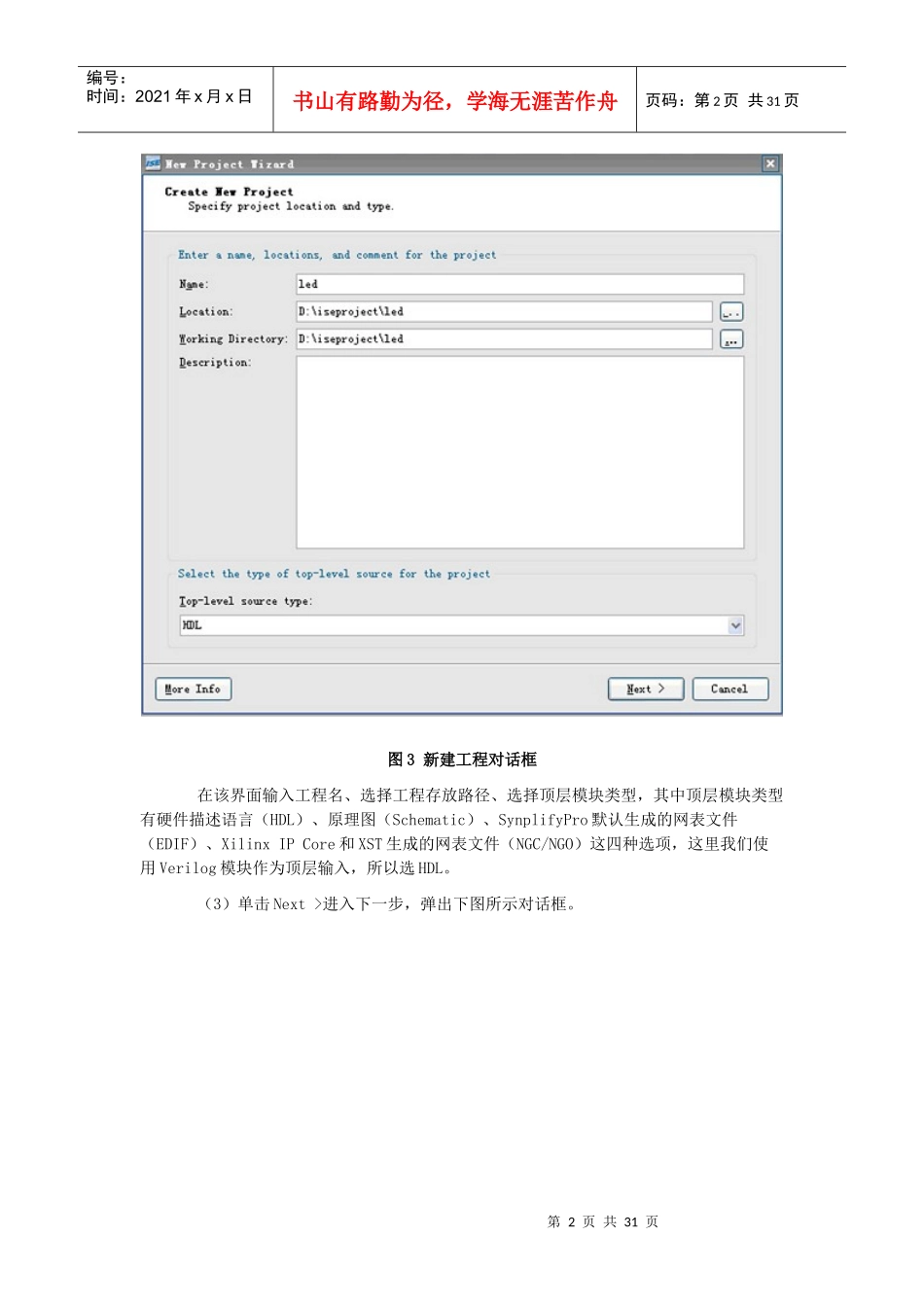

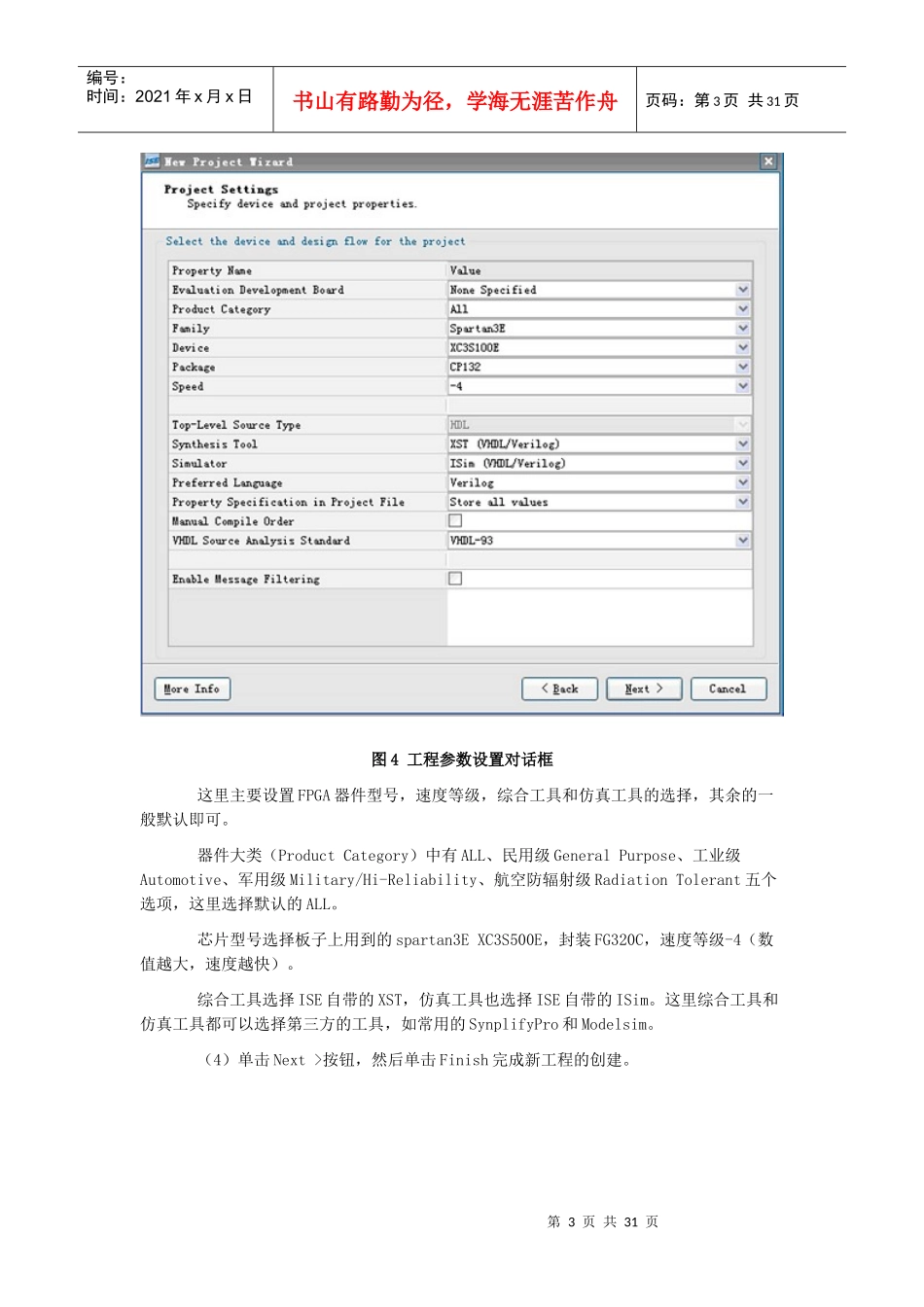

第1页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共31页基于ISE12.4的FPGA设计基本流程ISE是使用XILINX的FPGA的必备的设计工具,它可以完成FPGA开发的全部流程,包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。本文主要通过一个最简单的“点亮LED灯”实例介绍了基于ISE12.4软件的FPGA设计流程,包括设计输入、仿真、约束、下载等。0前言一套完整的FPGA设计流程包括电路设计输入、功能仿真、设计综合、综合后仿真、设计实现、添加约束、布线后仿真和下载、调试等主要步骤。图1FPGA设计流程目前赛灵思公司FPGA设计软件的最新版本是ISE13.1,本文中以ISE12.4为例。ISE9以后的版本的安装文件都是集成到了一个包当中,安装起来很方便。软件包里面包含四个大的工具,ISEDesignTools、嵌入式设计工具EDK、PlanAhead、XtremeDSP设计工具SystemGenerator。ISE设计工具中包含ISEProjectNavigator、ChipScopePro和以下工具:图2ISE软件包中部分工具做一般的FPGA逻辑设计时只需要用到ISE设计工具,下面通过一个最简单的“点亮LED灯”实例,具体讲解ISE设计工具的使用,并介绍基于ISE的FPGA设计基本流程。1创建工程(1)在桌面快捷方式或开始→所有程序→XilinxISEDesignSuite12.4→ISEDesignTools中打开ISEProjectNavigator。(2)单击File→NewProject...出现下图所示对话框。第2页共31页第1页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共31页图3新建工程对话框在该界面输入工程名、选择工程存放路径、选择顶层模块类型,其中顶层模块类型有硬件描述语言(HDL)、原理图(Schematic)、SynplifyPro默认生成的网表文件(EDIF)、XilinxIPCore和XST生成的网表文件(NGC/NGO)这四种选项,这里我们使用Verilog模块作为顶层输入,所以选HDL。(3)单击Next>进入下一步,弹出下图所示对话框。第3页共31页第2页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第3页共31页图4工程参数设置对话框这里主要设置FPGA器件型号,速度等级,综合工具和仿真工具的选择,其余的一般默认即可。器件大类(ProductCategory)中有ALL、民用级GeneralPurpose、工业级Automotive、军用级Military/Hi-Reliability、航空防辐射级RadiationTolerant五个选项,这里选择默认的ALL。芯片型号选择板子上用到的spartan3EXC3S500E,封装FG320C,速度等级-4(数值越大,速度越快)。综合工具选择ISE自带的XST,仿真工具也选择ISE自带的ISim。这里综合工具和仿真工具都可以选择第三方的工具,如常用的SynplifyPro和Modelsim。(4)单击Next>按钮,然后单击Finish完成新工程的创建。第4页共31页第3页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第4页共31页图5新建工程概要该窗口会显示新建工程的概要,核对无误后点击Finish完成工程创建。在工作区可看到新建的工程LED。第5页共31页第4页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第5页共31页2设计输入(1)在源代码窗口中单击右键,在弹出的菜单中选择NewSource。图6新建源文件向导第6页共31页第5页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第6页共31页在源文件类型中选择VerilogModule,输入文件名,其余使用软件默认即可。(2)单击Next>按钮,弹出的窗口是模块创建向导界面,这里我们不使用该功能,直接单击单击Next>按钮到下一步,点击Finish完成新源文件的创建。图7模块创建向导界面(3)ISE会自动打开源代码编辑界面,在该界面输入源代码,点击保存。第7页共31页第6页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第7页共31页图8源代码编辑界面在该界面下,我们输入以下源代码。这段代码的功能就是点亮一个LED灯,让它闪烁起来。选用板子上的一个50MHZ的晶振,对其进行分频后达到人眼能够辨别的跳变速率。第8页共31页第7页共31页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第8页共31页3功能仿真(1)加入仿真激励源...