八位十进制数字频率计一、设计任务(1)熟悉Quatus11软件的基本使用方法

(2)熟悉EDA实验开发系统的使用方法

(3)学习时序电路的设计、仿真和硬件设计,进一步熟悉VHDL设计技术

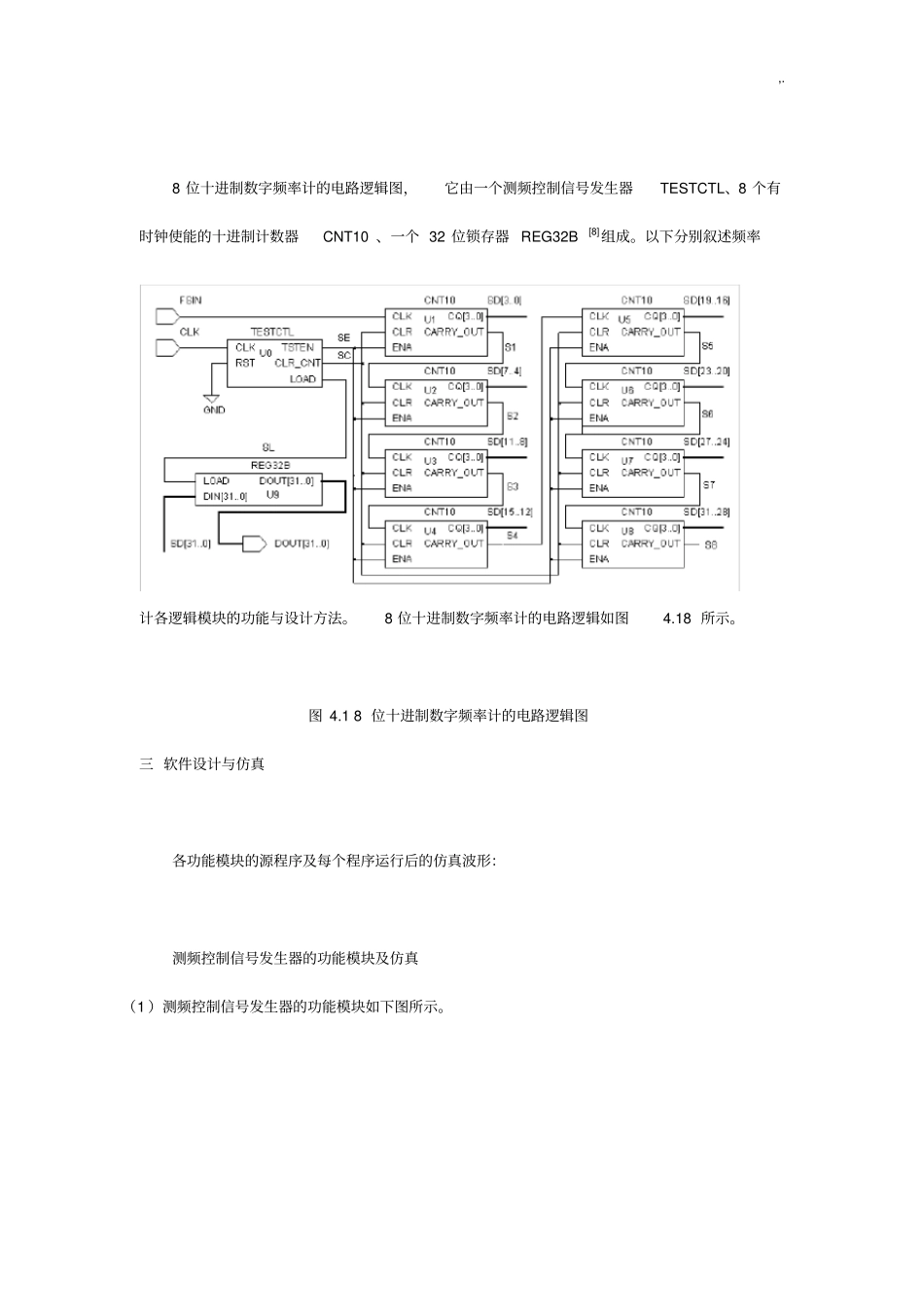

(4)分析了8位十进制数字频率计的基本原理

(5)对数字频率计的各个模块功能的分析,进行了功能仿真测试,得出仿真波形图

二、方案选择与设计数字频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,通常情况下计算每秒内待测信号的脉冲个数,此时我们称闸门时间为1秒

闸门时间也可以大于或小于一秒

闸门时间越长,得到的频率值就越准确,但闸门时间越长则每测一次频率的间隔就越长

闸门时间越短,测的频率值刷新就越快,但测得的频率精度就受影响

数字频率计的主要功能是测量周期信号的频率

频率是单位时间(1S)内信号发生周期变化的次数

如果我们能在给定的1S时间内对信号波形计数,并将计数结果显示出来,就能读取被测信号的频率

数字频率计首先必须获得相对稳定与准确的时间,同时将被测信号转换成幅度与波形均能被数字电路识别的脉冲信号,然后通过计数器计算这一段时间间隔内的脉冲个数,将其换算后显示出来

这就是数字频率计的基本原理

1)脉冲信号的频率就是在单位时间内所产生的脉冲个数,其表达式为,f为被测信号的频率,N为计数器所累积的脉冲个数,T为产生N个脉冲所需的时间

所以,在1秒时间内计数器所记录的结果,就是被测信号的频率

2)被测频率信号取自实验箱晶体振荡器输出信号,加到主控室的输入端

3)再取晶体振荡器的另一标准频率信号,经分频后产生各种时基脉冲:1ms,10ms,0

1s,1s等,时基信号的选择可以控制,即量程可以改变

4)时基信号经控制电路产生闸门信号至主控门,只有在闸门信号采样期间内(时基信号的一个周期),输入信号才通过主控门

5)f=N/T,改变时基信号的周期T,即可得到不同的测频范围