NextGenerationSubstrateTechnology–EmbeddedActiveIC前言:英特爾負責XScale處理器核心設計的設計經理黑柏(JayHebb)在2003國際固態電路會議(ISSCC)中,宣告SoC發展已死,因為要將數位邏輯、記憶體、類比等功能整合在同一晶片中,所需要的額外光罩製程過多,成本也過高,是SoC發展的最大阻力

也因為如此,SysteminPackage(SiP)系統級構裝便成為先進構裝實現輕薄短小化之最佳選擇

以往印刷電路板技術主要是承載線路,近年來隨著SiP的發展,已成功將被動元件內埋到基板內,而主動元件內埋則成為目前產學研積極研究之目標,藉由元件的內埋化,可使構裝面積/體積大幅度縮小,達到電子產品輕薄短小化、高功能化、高速化及高密度化之需求

在「基板內埋主動元件」技術發展上,美國Intel與GE、日本Casio與CMK、德國IZM均已投入多年研發;國內研究機構ITRI(工研院)及基板廠如PPT(全懋)也相繼積極投入研發;國內其他廠商也均密切注意此技術之進展

工研院電子所「先進微系統與構裝技術中心(AMPC)」有鑑於「基板內埋主動元件」技術如雨後春筍般的發展,特別邀請德國FraunhoferIZM專家AndreasOstmann、日本構裝市場分析專家Henry、國內產業界專家、工研院材料所及電子所專家,針對此議題作深入探討,希望能提供與會者在「基板內埋主動元件」技術研發方向的參考及產學研間的互動,創造更多的合作機制,以提升台灣在System-in-Package的整體能力

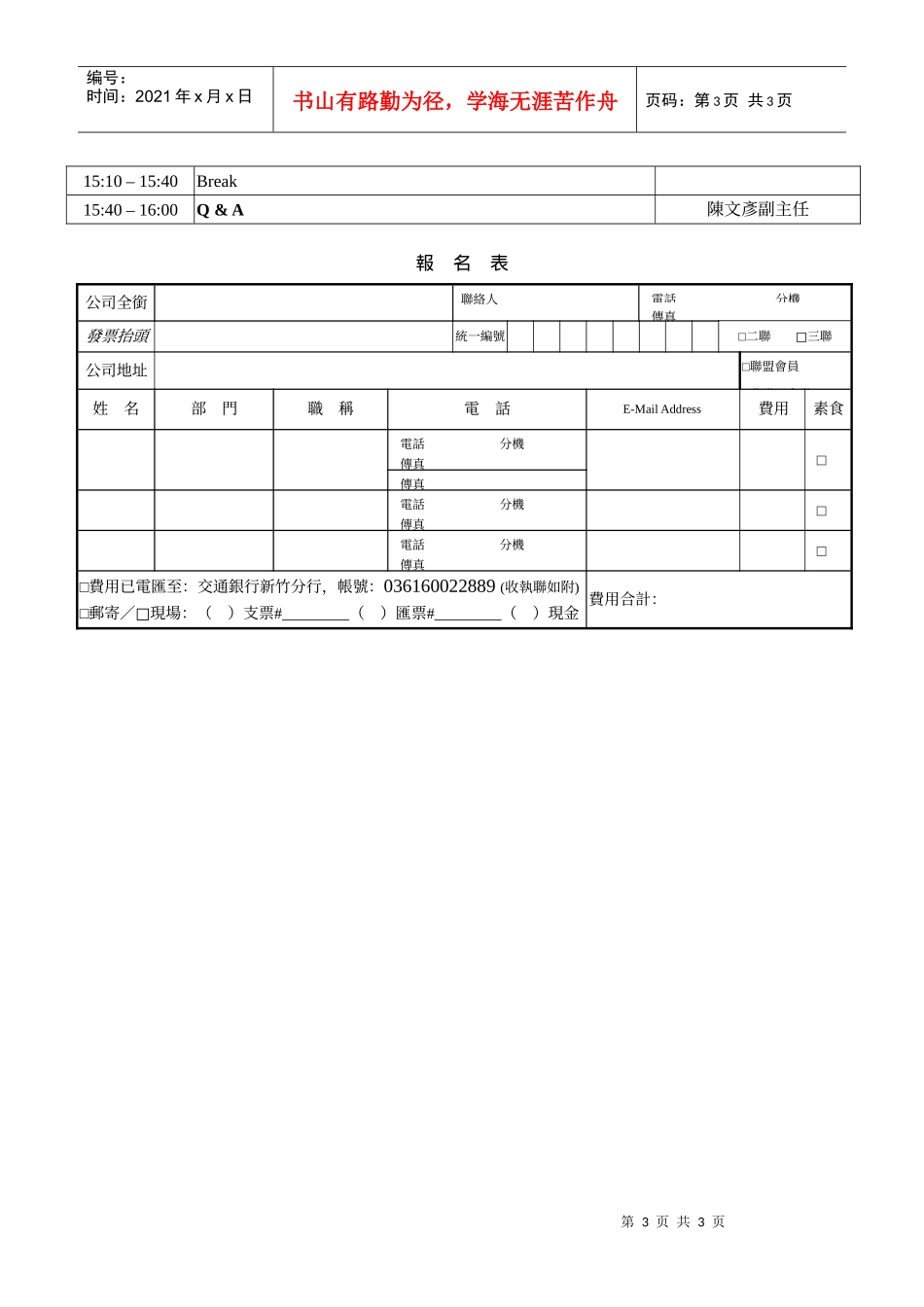

時間:94年5月19日與5月20日(星期四、五)9:00至16:30地點:工研院9館010會議室(新竹縣竹東鎮中興路四段195號,電話︰03-5918062)主辦單位:工業技術研究院電子工業研究所協辦單位:先進微系統與構裝技術聯盟講師群:講師如議程所列參加對象: