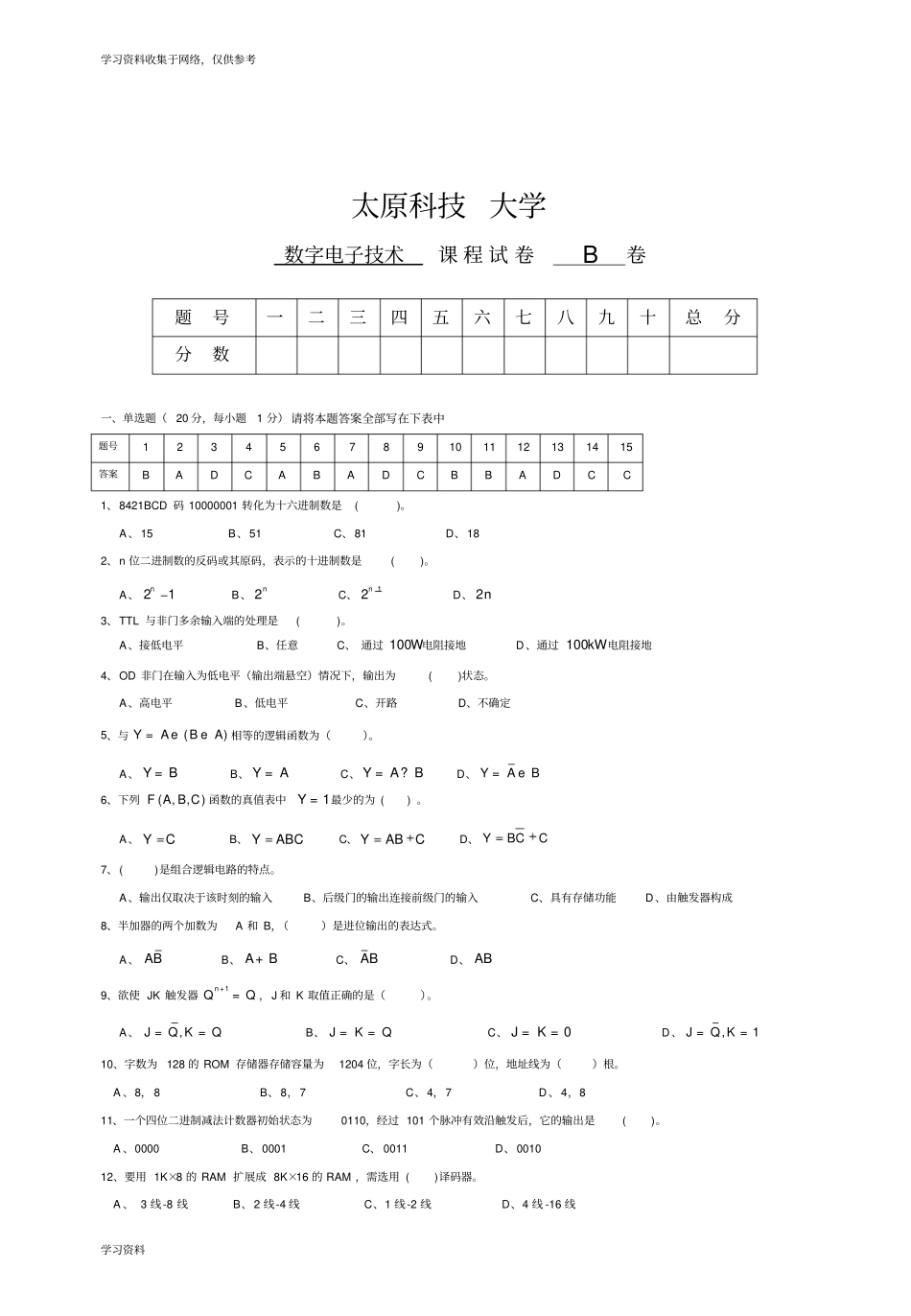

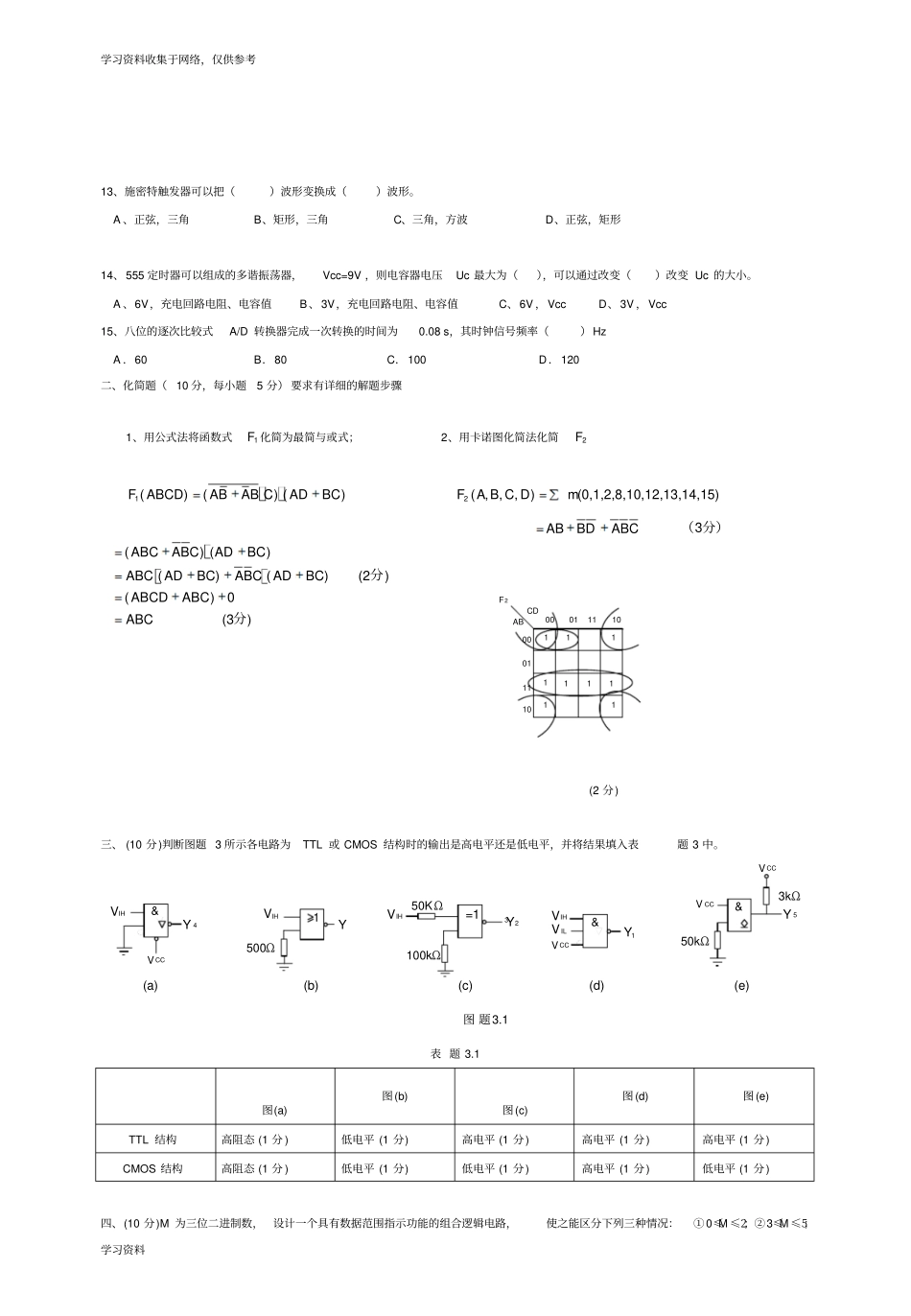

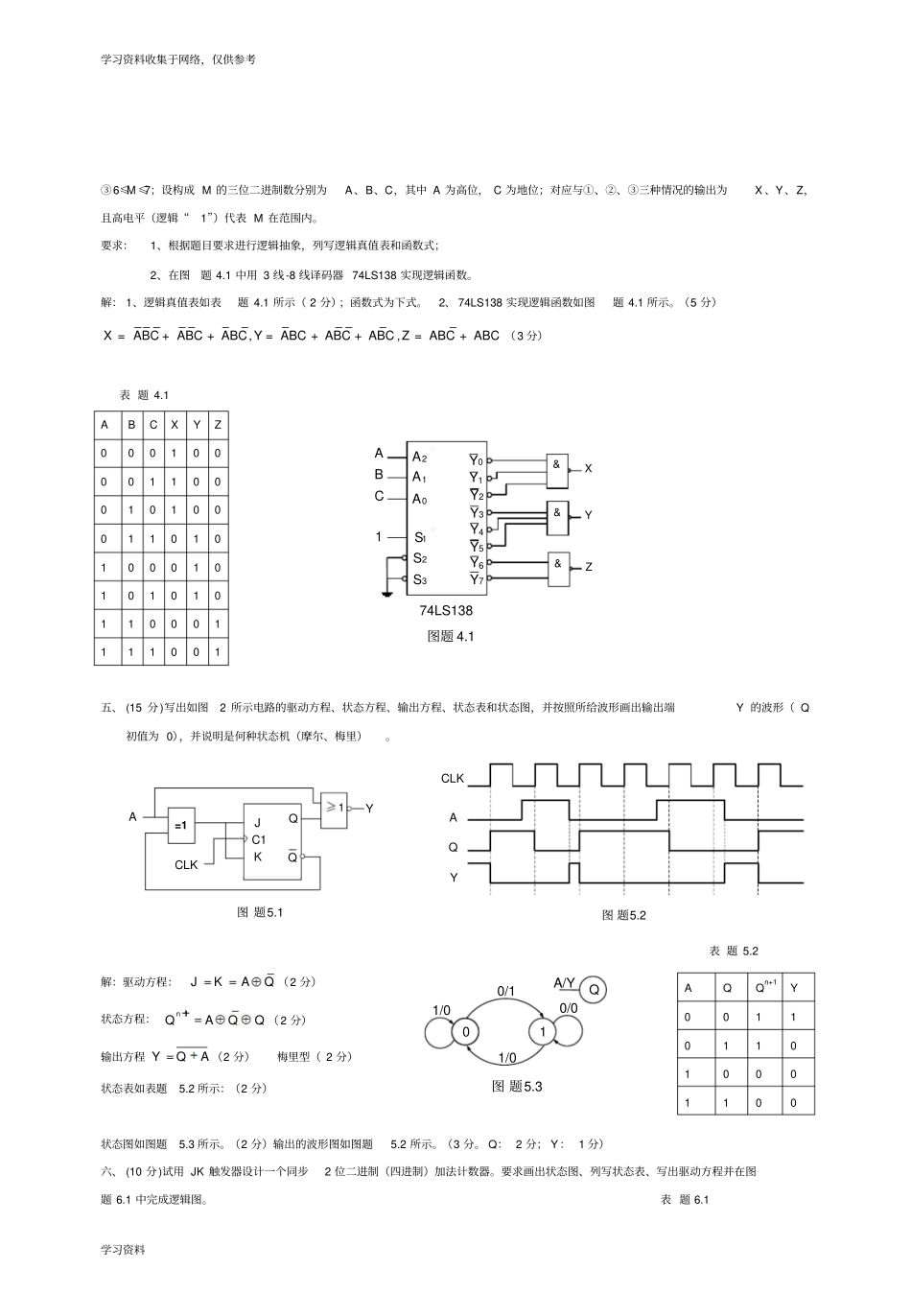

学习资料收集于网络,仅供参考学习资料太原科技大学数字电子技术课程试卷B卷一、单选题(20分,每小题1分)请将本题答案全部写在下表中题号123456789101112131415答案BADCABADCBBADCC1、8421BCD码10000001转化为十六进制数是()。A、15B、51C、81D、182、n位二进制数的反码或其原码,表示的十进制数是()。A、21nB、2nC、12nD、2n3、TTL与非门多余输入端的处理是()。A、接低电平B、任意C、通过100W电阻接地D、通过100kW电阻接地4、OD非门在输入为低电平(输出端悬空)情况下,输出为()状态。A、高电平B、低电平C、开路D、不确定5、与()YABA=ee相等的逻辑函数为()。A、YB=B、YA=C、YAB=?D、YAB=e6、下列(,,)FABC函数的真值表中1Y=最少的为()。A、YCB、YABCC、YABCD、YBCC7、()是组合逻辑电路的特点。A、输出仅取决于该时刻的输入B、后级门的输出连接前级门的输入C、具有存储功能D、由触发器构成8、半加器的两个加数为A和B,()是进位输出的表达式。A、ABB、AB+C、ABD、AB9、欲使JK触发器1nQQ+=,J和K取值正确的是()。A、,JQKQ==B、JKQ==C、0JK==D、,1JQK==10、字数为128的ROM存储器存储容量为1204位,字长为()位,地址线为()根。A、8,8B、8,7C、4,7D、4,811、一个四位二进制减法计数器初始状态为0110,经过101个脉冲有效沿触发后,它的输出是()。A、0000B、0001C、0011D、001012、要用1K×8的RAM扩展成8K×16的RAM,需选用()译码器。A、3线-8线B、2线-4线C、1线-2线D、4线-16线题号一二三四五六七八九十总分分数学习资料收集于网络,仅供参考学习资料13、施密特触发器可以把()波形变换成()波形。A、正弦,三角B、矩形,三角C、三角,方波D、正弦,矩形14、555定时器可以组成的多谐振荡器,Vcc=9V,则电容器电压Uc最大为(),可以通过改变()改变Uc的大小。A、6V,充电回路电阻、电容值B、3V,充电回路电阻、电容值C、6V,VccD、3V,Vcc15、八位的逐次比较式A/D转换器完成一次转换的时间为0.08s,其时钟信号频率()HzA.60B.80C.100D.120二、化简题(10分,每小题5分)要求有详细的解题步骤1、用公式法将函数式1F化简为最简与或式;2、用卡诺图化简法化简2F1()()()FABCDABABCADBC(2分)三、(10分)判断图题3所示各电路为TTL或CMOS结构时的输出是高电平还是低电平,并将结果填入表题3中。&=1IHV50KΩ1500ΩIHVVCCIHV&3kΩVCC50kΩVCCY2Y3Y4Y5(a)(b)(d)(c)图题3.1&VCCIHVYILV(e)1100kΩ表题3.1图(a)图(b)图(c)图(d)图(e)TTL结构高阻态(1分)低电平(1分)高电平(1分)高电平(1分)高电平(1分)CMOS结构高阻态(1分)低电平(1分)低电平(1分)高电平(1分)低电平(1分)四、(10分)M为三位二进制数,设计一个具有数据范围指示功能的组合逻辑电路,使之能区分下列三种情况:①0≤M≤2;②3≤M≤5;()()()()(2)()0(3)ABCABCADBCABCADBCABCADBCABCDABCABC分分2(,,,)(0,1,2,8,10,12,13,14,15)FABCDmABBDABC(3分)F2ABCD0001111000011110111111111学习资料收集于网络,仅供参考学习资料③6≤M≤7;设构成M的三位二进制数分别为A、B、C,其中A为高位,C为地位;对应与①、②、③三种情况的输出为X、Y、Z,且高电平(逻辑“1”)代表M在范围内。要求:1、根据题目要求进行逻辑抽象,列写逻辑真值表和函数式;2、在图题4.1中用3线-8线译码器74LS138实现逻辑函数。解:1、逻辑真值表如表题4.1所示(2分);函数式为下式。2、74LS138实现逻辑函数如图题4.1所示。(5分),,XABCABCABCYABCABCABCZABCABC=++=++=+(3分)表题4.1五、(15分)写出如图2所示电路的驱动方程、状态方程、输出方程、状态表和状态图,并按照所给波形画出输出端Y的波形(Q初值为0),并说明是何种状态机(摩尔、梅里)。C1JK=11AYCLKQQ图题5.1CLKAQ图题5.2Y表题5.2解:驱动方程:JKAQ(2分)状态方程:1nQAQQ(2分)输出方程YQA(2分)梅里型(2分)状态表如表题5.2所示:(2分)状态图如图题5.3所示。(2分)输出的波形图如图题5.2所示。(3分。Q:2分;Y:1分)六、(10分)试用JK触发器设计一个同步2位二进制(四进制)加法计数器。要求画出状态图、列写状态表、写出驱动方程并在图题6.1中完成逻辑图。表题6.1ABCXYZ0001...