袖钟输出1CP0Q01BE丄一、实验目的1

熟悉集成计数器的逻辑功能和各控制端的作用

掌握计数器的使用方法

掌握任意进制计数器的设计方法

了解8421BCD和5421BCD的编码规则

二、实验器材集成计数器74LS90、四2输入与非门74LS00、双4输入与非门74LS20、四异或门74LS86、六非门74LS04、显示译码器7447/7448、七段数码管三、实验任务及要求1

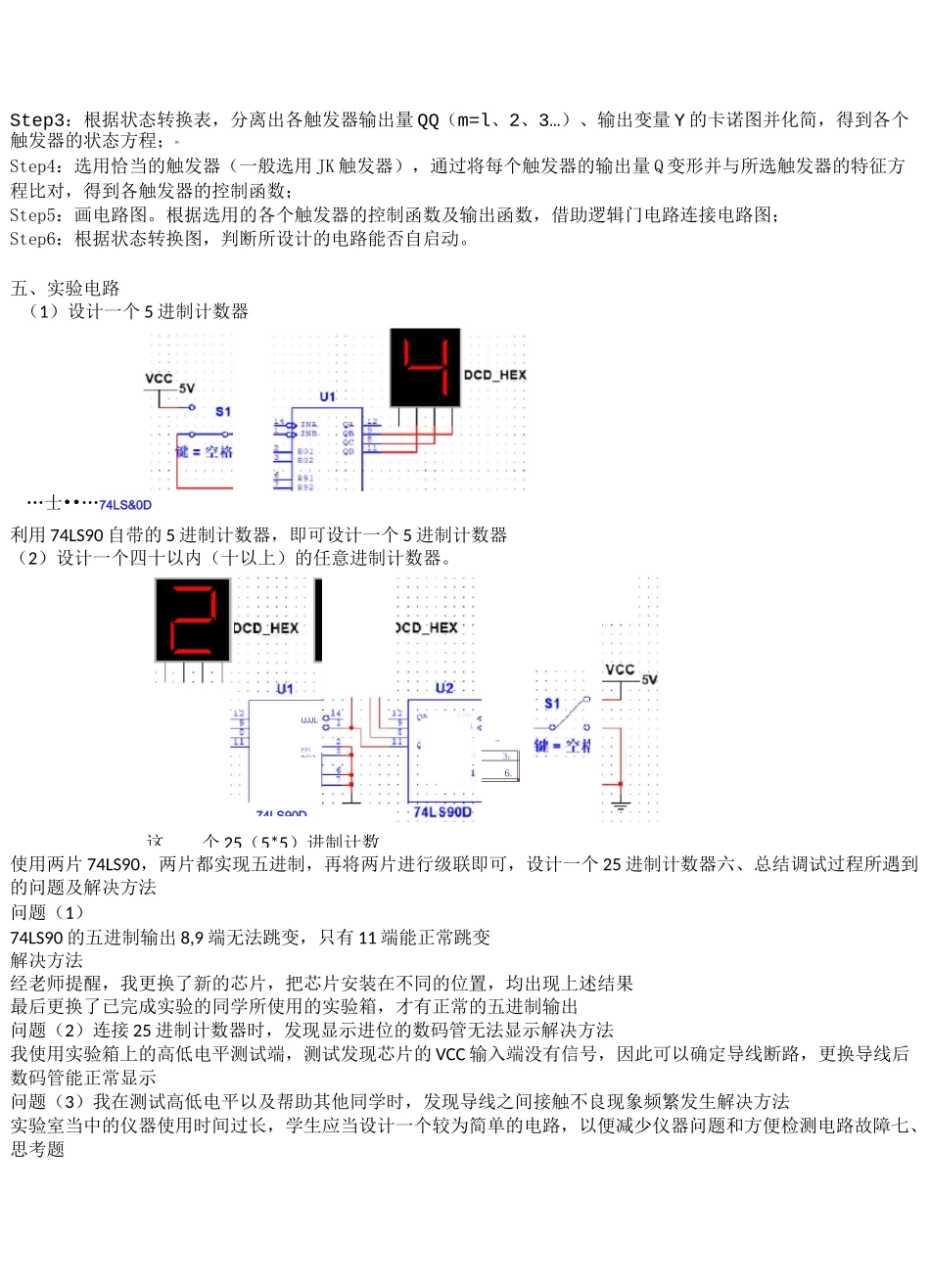

设计要求(1)用1片74LS90和1片与非门设计一个5进制计数器

(2)用2片74LS90和1片与非门设计一个四十以内(十以上)的任意进制计数器

实验内容(1)测试所用芯片74LS90的逻辑功能(置0、置9、8421BCD计数输出功能)

(2)组装所设计的时序逻辑电路,并验证其功能是否正确

提示:计数器的状态输出端分别接在实验箱上的显示译码器的输入端,用七段数码管显示计数状态值

CP接实验箱上的可调连续脉冲

飞时序逻辑电路的设计QjGND4567二进CPT»NC爲四、实验原理1

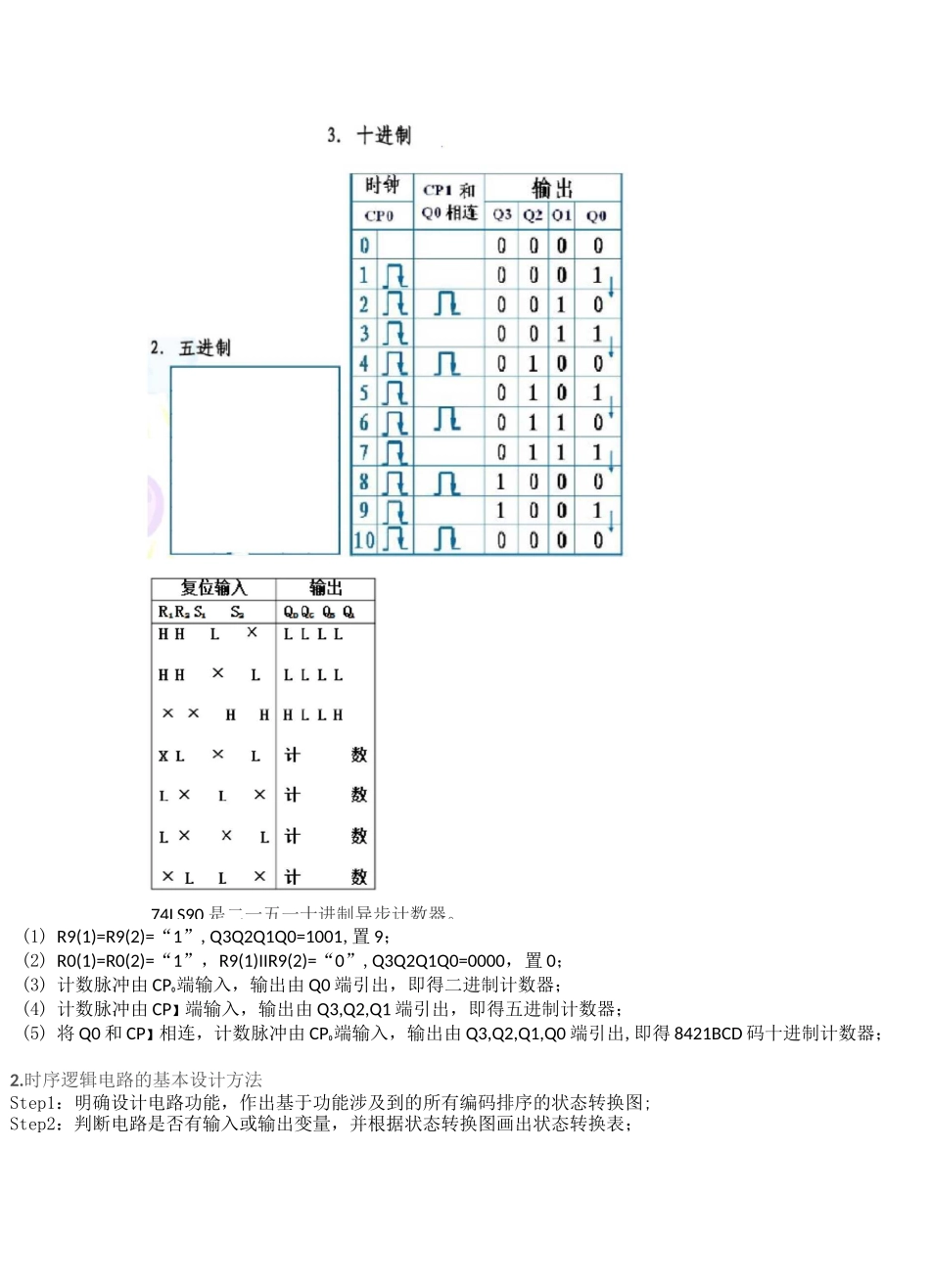

74LS90的逻辑功4集成计数的引脚图CPIRO(i)RO(2)NVCCR9(i)R9五进制时钟信入豐9n二进制时」鞅信号123M98计数输时钟输出CP1Q3Q2QI00001A0012n010304r1005n0Q0(1)R9(1)=R9(2)=“1”,Q3Q2Q1Q0=1001,置9;(2)R0(1)=R0(2)=“1”,R9(1)IIR9(2)=“0”,Q3Q2Q1Q0=0000,置0;(3)计数脉冲由CP0端输入,输出由Q0端引出,即得二进制计数器;(4)计数脉冲由CP】端输入,输出由Q3,Q2,Q1端引出,即得五进制计数器;(5)将Q0和CP】相连,计数脉冲由CP0端输入,输出由Q3,Q2,Q1,Q0端引出,即得8421BCD码十进制计数器;2

时序逻辑电路的基本设计方法Step1:明确设计电路功能,