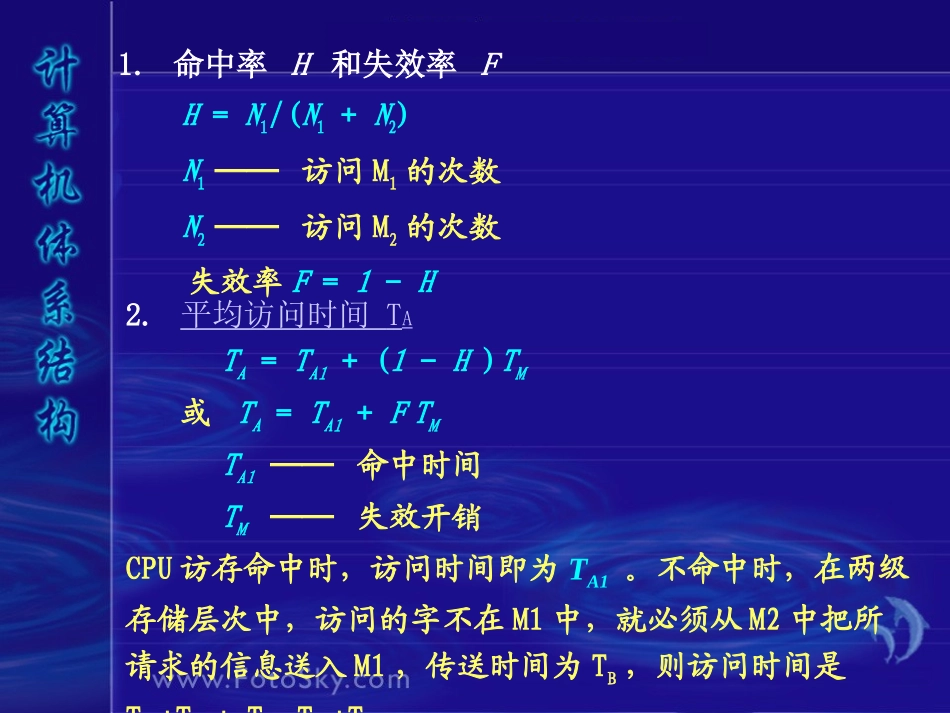

平均访问时间TATA=TA1+(1-H)TM或TA=TA1+FTMTA1──命中时间TM──失效开销CPU访存命中时,访问时间即为TA1

不命中时,在两级存储层次中,访问的字不在M1中,就必须从M2中把所请求的信息送入M1,传送时间为TB,则访问时间是TA2+TB+TA1=TA1+TM

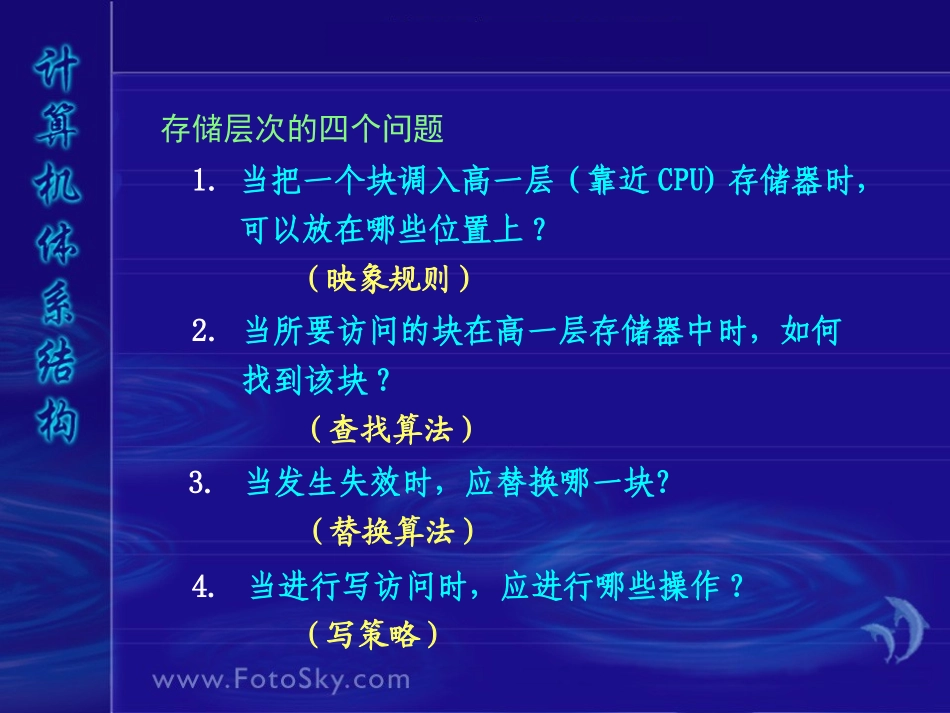

命中率H和失效率FH=N1/(N1+N2)N1──访问M1的次数N2──访问M2的次数失效率F=1-H存储层次的四个问题当把一个块调入高一层(靠近CPU)存储器时,可以放在哪些位置上

(映象规则)当所要访问的块在高一层存储器中时,如何找到该块

(查找算法)3

当发生失效时,应替换哪一块

(替换算法)4

当进行写访问时,应进行哪些操作

(写策略)1

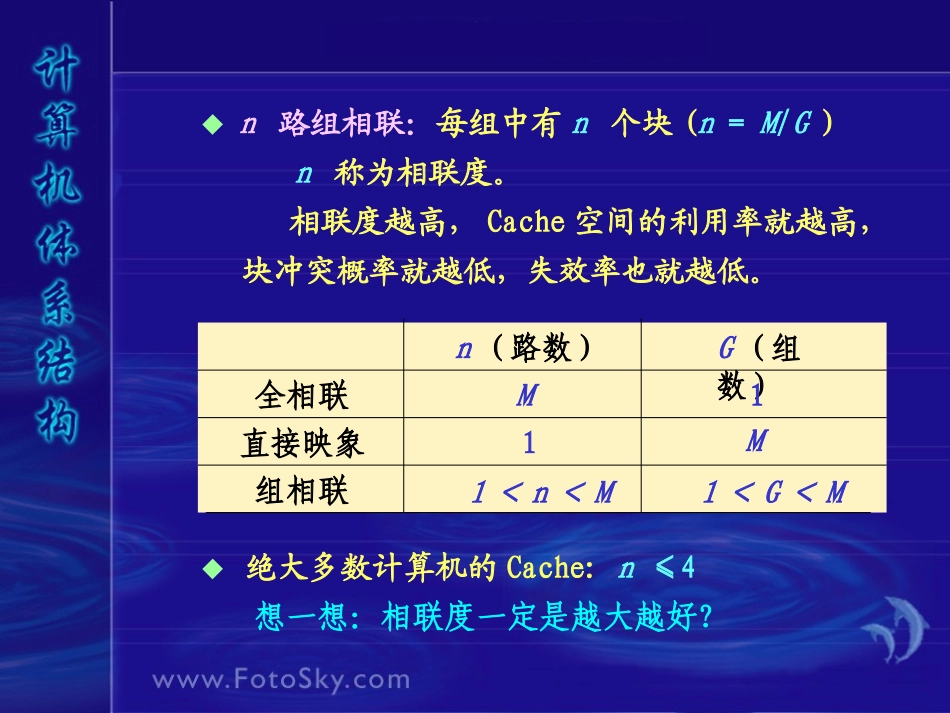

◆绝大多数计算机的Cache:n≤4想一想:相联度一定是越大越好

◆n路组相联:每组中有n个块(n=M/G)n称为相联度

相联度越高,Cache空间的利用率就越高,块冲突概率就越低,失效率也就越低

全相联直接映象组相联n(路数)G(组数)MM111<n<M1<G<M3

1性能分析2

平均访问时间平均访问时间=命中时间+失效率×失效开销例假设Cache的命中时间为1个时钟周期,失效开销为50个时钟周期,在混合Cache中一次load或store操作访问Cache的命中时间都要增加一个时钟周期(因为混合Cache只有一个端口,无法同时满足两个请求

按照有关流水线的术语,混合Cache会导致结构冲突),试问指令Cache和数据Cache容量均为16KB的分离Cache和容量为32KB的混合Cache相比,哪种Cache的失效率更低

又假设采用写直达策略,且有一个写缓冲器,并且忽略写缓冲器引起的等待

请问上述两种情况下平均访存时间各是多少

失效率混合Cache与分离Cache分离Cache平均失效率的计算:访问指令Cache的百分比×指