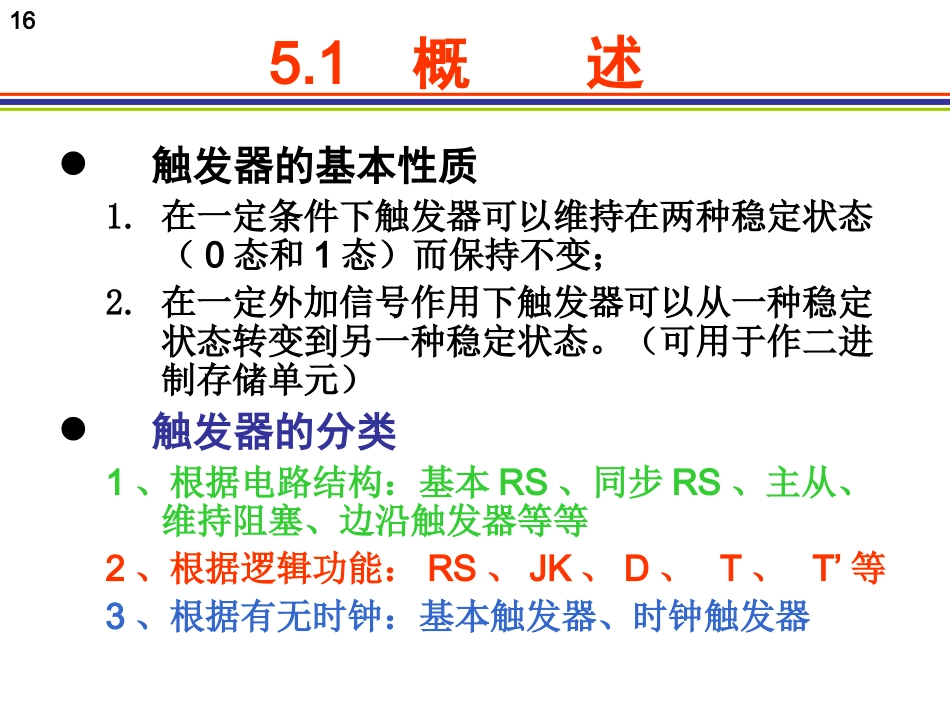

1概述触发器的基本性质1

在一定条件下触发器可以维持在两种稳定状态(0态和1态)而保持不变;2

在一定外加信号作用下触发器可以从一种稳定状态转变到另一种稳定状态

(可用于作二进制存储单元)触发器的分类1、根据电路结构:基本RS、同步RS、主从、维持阻塞、边沿触发器等等2、根据逻辑功能:RS、JK、D、T、T’等3、根据有无时钟:基本触发器、时钟触发器16触发器触发器输出有两种可能的状态:0、1;输出状态不只与现时的输入有关,还与原来的输出状态有关;触发器是有记忆功能的逻辑部件

5-2基本(双稳态)触发器Q,Q输出端1

基本的R-S触发器组成:用2个与非门构成5

1由与非门组成的R-S触发器&&RDSDQQSD—SET直接置位端RD—RESET直接复位端逻辑符号RDSDQQ0101(复位)1010(置位)11保持原状00不确定&&RDSDQQR-S触发器真值表(特性表)011100RD=0同时SD=1时,Q=0

故RD称为复位端,或称为清0端&&RDSDQQRDSDQQ0101(复位)1010(置位)11保持原状00不确定R-S触发器真值表(特性表)011100SD=0同时RD=1时,Q=1

故SD称为置位端,或称为置1端RDSDQQ0101(复位)1010(置位)11保持原状00不确定&&RDSDQQR-S触发器真值表110011指R、S从01或10变成11时,输出端状态不变&&RDSDQQR-S触发器真值表RDSDQQ0101(复位)1010(置位)11保持原状00不确定指RD、SD同时从00变成11时,输出端状态不定001111R-S触发器真值表RDSDQQ0101(复位)1010(置位)11保持原状00不确定指RD、SD同时从00变成11时,输出端状态不定&&RDSDQQ00111111&&RDSDQQ001111110000即Q