1分立元件门电路13

3CMOS门电路13

2TTL门电路第13章门电路和组合逻辑电路13

4组合逻辑电路的分析13

5加法器13

6编码器13

7译码器和数字显示13

8半导体存储器和可编程逻辑器件13

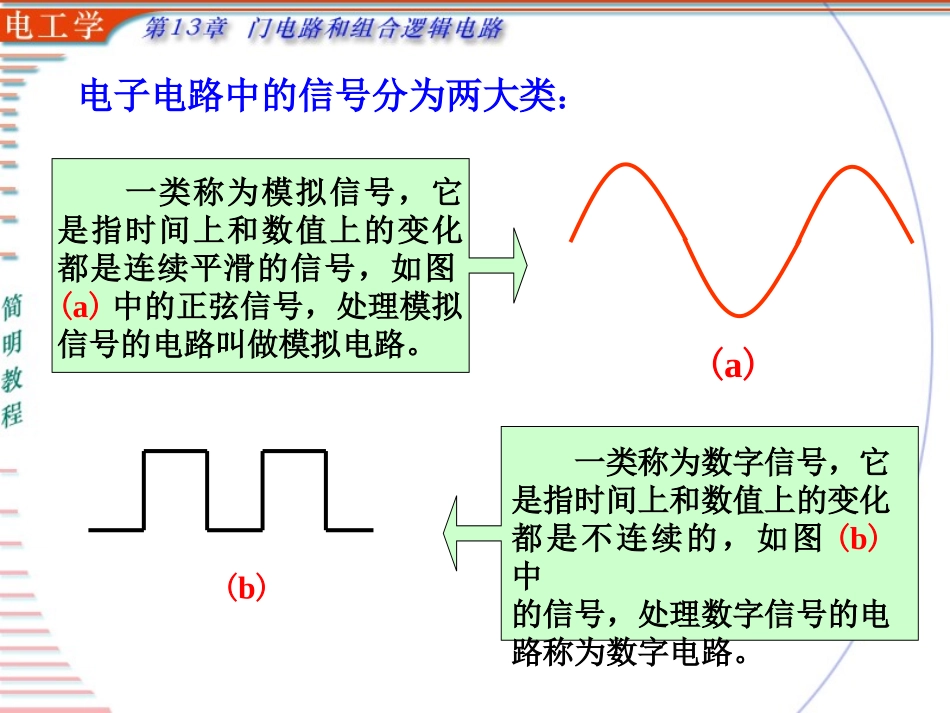

9应用举例一类称为模拟信号,它是指时间上和数值上的变化都是连续平滑的信号,如图(a)中的正弦信号,处理模拟信号的电路叫做模拟电路

电子电路中的信号分为两大类:一类称为数字信号,它是指时间上和数值上的变化都是不连续的,如图(b)中的信号,处理数字信号的电路称为数字电路

(b)(a)13

1门电路的基本概念13

1分立元件门电路门电路:实现各种逻辑关系的电路分析逻辑电路时只用两种相反的工作状态,并用1或0表示

如开关接通用1表示,开关断开用0表示

灯亮可用1表示,灯灭可用0表示

正逻辑系统:高电位用1表示,低电位用0表示

负逻辑系统:高电位用0表示,低电位用1表示

2二极管与门电路+12VABCDADBDC设:uA=0,uB=uC=3V则DA导通,DB、DC截止

3VuY=0

3VYRY=0uA,uB,uC中任意一个或两个为0,Y=0设:3V为高电位1,0

3V为低电位0,二极管管压降为0

+12VABCDADBDC设:uA=uB=uC=0DA、DB、DC都导通Y=0uY=0

3VYuY=0

3VRuY=3

3V设:uA=uB=uC=3VuY=3

3V,Y=1DA、DB、DC都导通+12VABCDADBDCYR由以上分析可知:只有当A、B、C全为高电平时,输出端才为高电平

正好符合与门的逻辑关系

与逻辑关系式:Y=ABCABCY&+12VABCDADBDCYR与门逻辑状态表与逻辑关系式:Y=ABCABCY&ABCY00000000000111100001111010101011设:uA=3V,uB=uC=0V则DA导通

uY=3–0