3组合逻辑电路设计2数字电子技术实验数字电子技术实验一、实验目的1

掌握使用中规模集成芯片译码器和数据选择器设计组合逻辑电路的方法

设计一个1位二进制全减器,要求:⑴用芯片74LS138译码器及74LS20“与非”门各一片实现

⑵用两片数据选择器74LS151芯片实现

二、实验任务3

用两片74LS138译码器实现一个4线-16线译码器

用74LS138译码器、74LS153数据选择器各一片实现一个可控的加、减运算电路

X=0时进行1位二进制加法运算;X=1时进行1位二进制减法运算

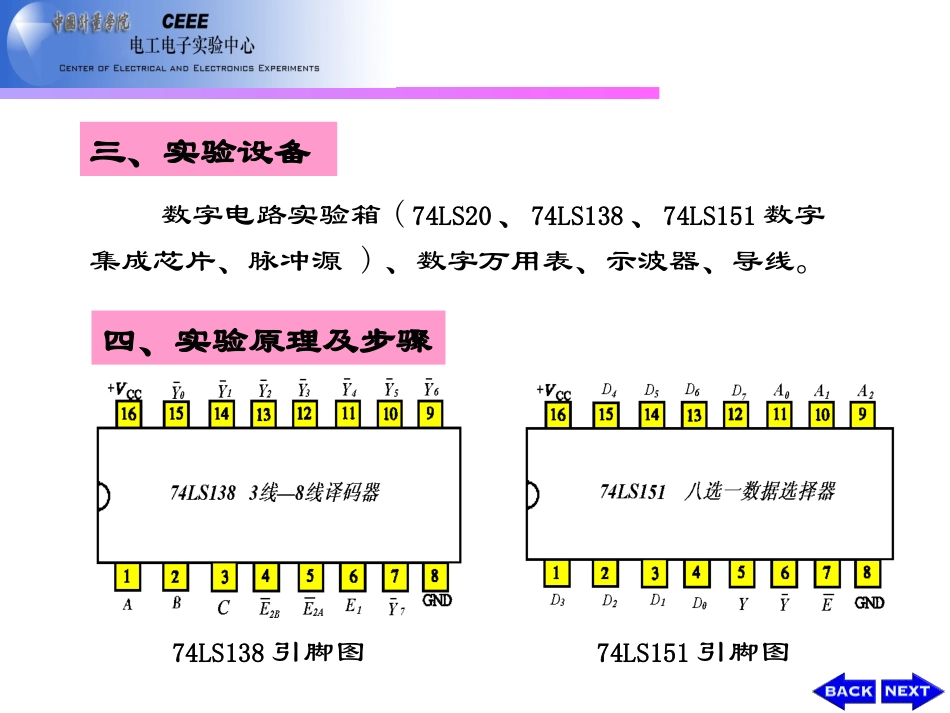

数字电路实验箱(74LS20、74LS138、74LS151数字集成芯片、脉冲源)、数字万用表、示波器、导线

三、实验设备四、实验原理及步骤74LS138引脚图74LS151引脚图74LS138逻辑符号输入输出端说明E1、:使能控制端,E1=1,AE2BE2022BAEE时芯片正常工作,输出与输入二进制码相对应,其它状态无译码输出

ABCY0ABCY1ABCY2BACY3ABCY4ABCY5ACBY6CBAY7C、B、A:输入端Y7~Y0:输出端(低电平有效)输入高位输入低位输入输出E1E2A+E2BCBAY7Y6Y5Y4Y3Y2Y1Y00×××××1×××10000100011001010011101001010110110101111111111111111111111111101111110111111011111101111110111111011111101111110111111174LS138功能表低电平有效输出端低电平有效按右图接线(输入接电平开关,输出接发光二极管),控制电平开关K1~K3,使得A2A1A0从000~111变化,输出二极管应为对应的一盏灯不亮(低电平输出)

亮灯情况符合功能表的芯片则为好的

根据74LS138功能表判断芯片好坏