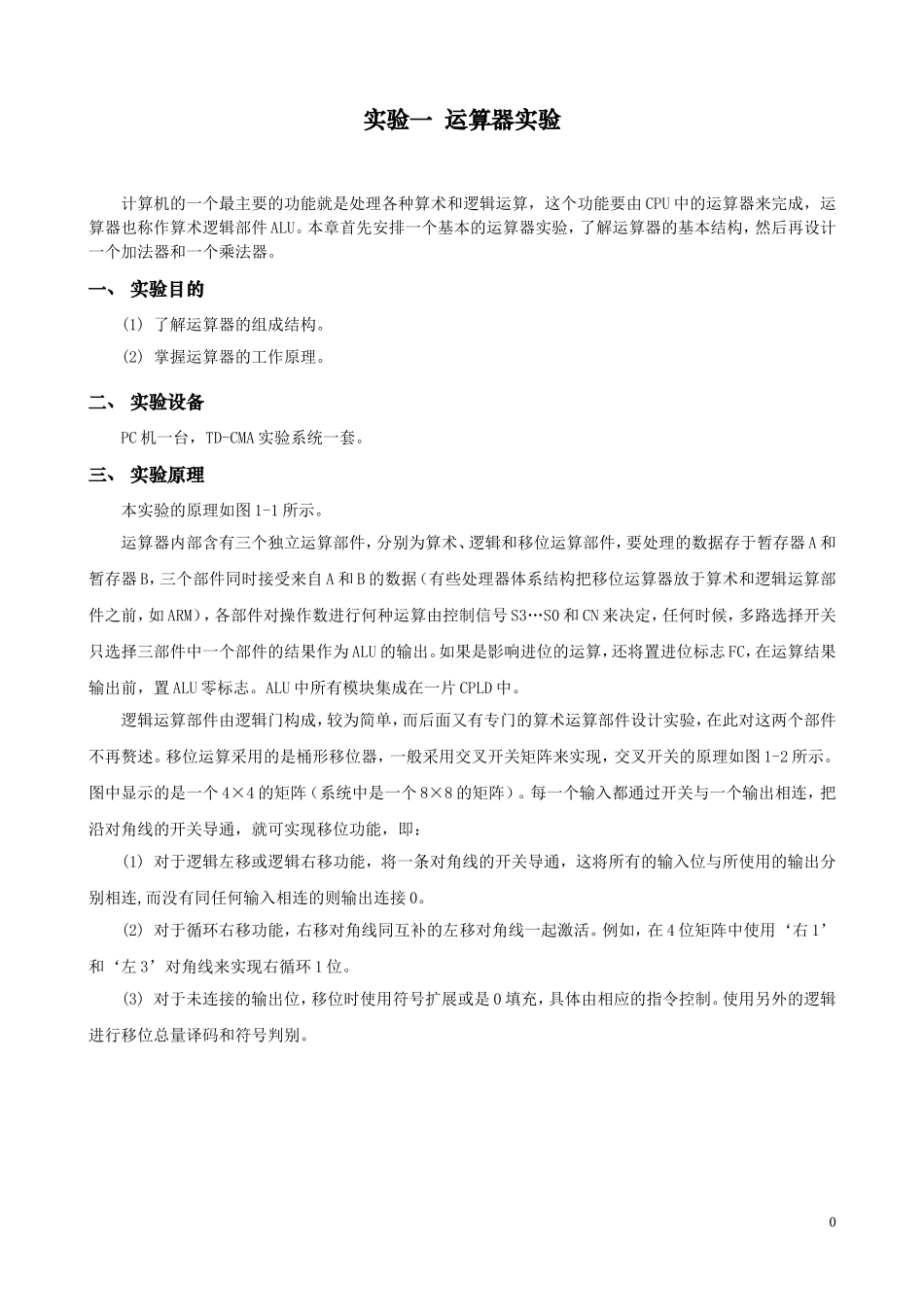

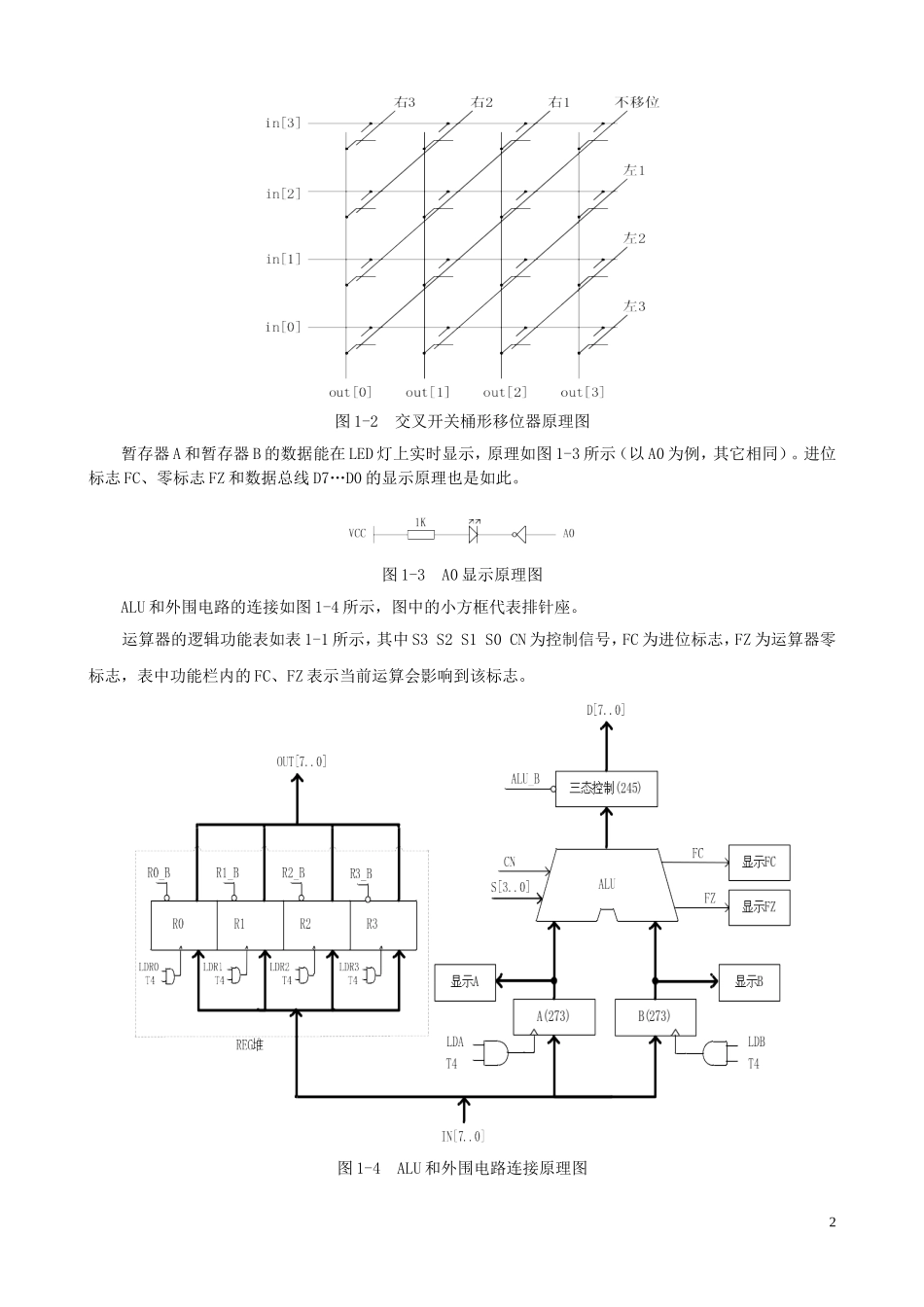

实验一运算器实验计算机的一个最主要的功能就是处理各种算术和逻辑运算,这个功能要由CPU中的运算器来完成,运算器也称作算术逻辑部件ALU。本章首先安排一个基本的运算器实验,了解运算器的基本结构,然后再设计一个加法器和一个乘法器。一、实验目的(1)了解运算器的组成结构。(2)掌握运算器的工作原理。二、实验设备PC机一台,TD-CMA实验系统一套。三、实验原理本实验的原理如图1-1所示。运算器内部含有三个独立运算部件,分别为算术、逻辑和移位运算部件,要处理的数据存于暂存器A和暂存器B,三个部件同时接受来自A和B的数据(有些处理器体系结构把移位运算器放于算术和逻辑运算部件之前,如ARM),各部件对操作数进行何种运算由控制信号S3…S0和CN来决定,任何时候,多路选择开关只选择三部件中一个部件的结果作为ALU的输出。如果是影响进位的运算,还将置进位标志FC,在运算结果输出前,置ALU零标志。ALU中所有模块集成在一片CPLD中。逻辑运算部件由逻辑门构成,较为简单,而后面又有专门的算术运算部件设计实验,在此对这两个部件不再赘述。移位运算采用的是桶形移位器,一般采用交叉开关矩阵来实现,交叉开关的原理如图1-2所示。图中显示的是一个4×4的矩阵(系统中是一个8×8的矩阵)。每一个输入都通过开关与一个输出相连,把沿对角线的开关导通,就可实现移位功能,即:(1)对于逻辑左移或逻辑右移功能,将一条对角线的开关导通,这将所有的输入位与所使用的输出分别相连,而没有同任何输入相连的则输出连接0。(2)对于循环右移功能,右移对角线同互补的左移对角线一起激活。例如,在4位矩阵中使用‘右1’和‘左3’对角线来实现右循环1位。(3)对于未连接的输出位,移位时使用符号扩展或是0填充,具体由相应的指令控制。使用另外的逻辑进行移位总量译码和符号判别。0图1-1运算器原理图运算器部件由一片CPLD实现。ALU的输入和输出通过三态门74LS245连到CPU内总线上,另外还有指示灯标明进位标志FC和零标志FZ。请注意:实验箱上凡丝印标注有马蹄形标记‘’,表示这两根排针之间是连通的。图中除T4和CLR,其余信号均来自于ALU单元的排线座,实验箱中所有单元的T1、T2、T3、T4都连接至控制总线单元的T1、T2、T3、T4,CLR都连接至CON单元的CLR按钮。T4由时序单元的TS4提供,其余控制信号均由CON单元的二进制数据开关模拟给出。控制信号中除T4为脉冲信号外,其余均为电平信号,其中ALU_B为低有效,其余为高有效。1图1-2交叉开关桶形移位器原理图暂存器A和暂存器B的数据能在LED灯上实时显示,原理如图1-3所示(以A0为例,其它相同)。进位标志FC、零标志FZ和数据总线D7…D0的显示原理也是如此。图1-3A0显示原理图ALU和外围电路的连接如图1-4所示,图中的小方框代表排针座。运算器的逻辑功能表如表1-1所示,其中S3S2S1S0CN为控制信号,FC为进位标志,FZ为运算器零标志,表中功能栏内的FC、FZ表示当前运算会影响到该标志。图1-4ALU和外围电路连接原理图2表1-1运算器逻辑功能表运算类型S3S2S1S0CN功能逻辑运算0000XF=A(直通)0001XF=B(直通)0010XF=AB(FZ)0011XF=A+B(FZ)0100XF=(FZ)移位运算0101XF=A不带进位循环右移B(取低3位)位(FZ)01100F=A逻辑右移一位(FZ)1F=A带进位循环右移一位(FC,FZ)01110F=A逻辑左移一位(FZ)1F=A带进位循环左移一位(FC,FZ)算术运算1000X置FC=CN(FC)1001XF=A加B(FC,FZ)1010XF=A加B加FC(FC,FZ)1011XF=A减B(FC,FZ)1100XF=A减1(FC,FZ)1101XF=A加1(FC,FZ)1110X(保留)1111X(保留)*表中“X”为任意态,下同四、实验步骤(1)按图1-5连接实验电路,并检查无误。图中将用户需要连接的信号用圆圈标明(其它实验相同)。图1-5实验接线图(2)将时序与操作台单元的开关KK2置为‘单步’档,开关KK1、KK3置为‘运行’档。(3)打开电源开关,3如果听到有‘嘀’报警声,说明有总线竞争现象,应立即关闭电源,重新检查接线,直到错误排除。然后按动CON单元的CLR按钮,将运算器的A、B和FC、FZ清零。(4)用输入开关向暂存器A置数。①拨动CON单元的SD27…SD20数据开关,形成二进制数01100101(或其它数值),数据显示亮为‘1’,灭为‘0’。②...