DCDC实测出来的纹波比公式计算出来的大,电容ESR的锅

我们设计DCDC电路的时候,经常会用下面的公式计算一下纹波输出电压,然后在输出端选择合适的电容

下面是某DCDC规格书的纹波说明:outputvoltageripplelow

Theoutputvoltageripplecanbeestimatedby:AVout'鬻卜[RE5H+爲心)辅出换公式WhereC2istheoutputcapacitancevatueandistheequivalentseriesresistance(ESR)valueaftheoutputcapacitor

Whenusingceramiccapacitors,theimpedance皿theswitchingfrequencyiwdcjmin日FEMby耒用遇江史容,迷出capacitancewhichisthemaincauseforlhe_宀宀耳

outputvoltageripple

Forsinnplification,the纹浪主要用电谷滋决outputvoltageripplecanbeestfmatedby:巧

陶瓷电容的ESR都说很小,可以忽略

那么根据输入输出电压,开关频率,目标纹波,就可以求得电容容量的大小

然而,不知道你发现没有,电路做出来实测一下,一般都比算出来的纹波要大,那么这是为什么呢

这是因为陶瓷电容的ESR实际不能忽略吗

而一般情况下我们并不知道电容ESR多大,所以就这样让陶瓷电容背锅了(我以前就是这么干的,汗)

那么真是这样吗

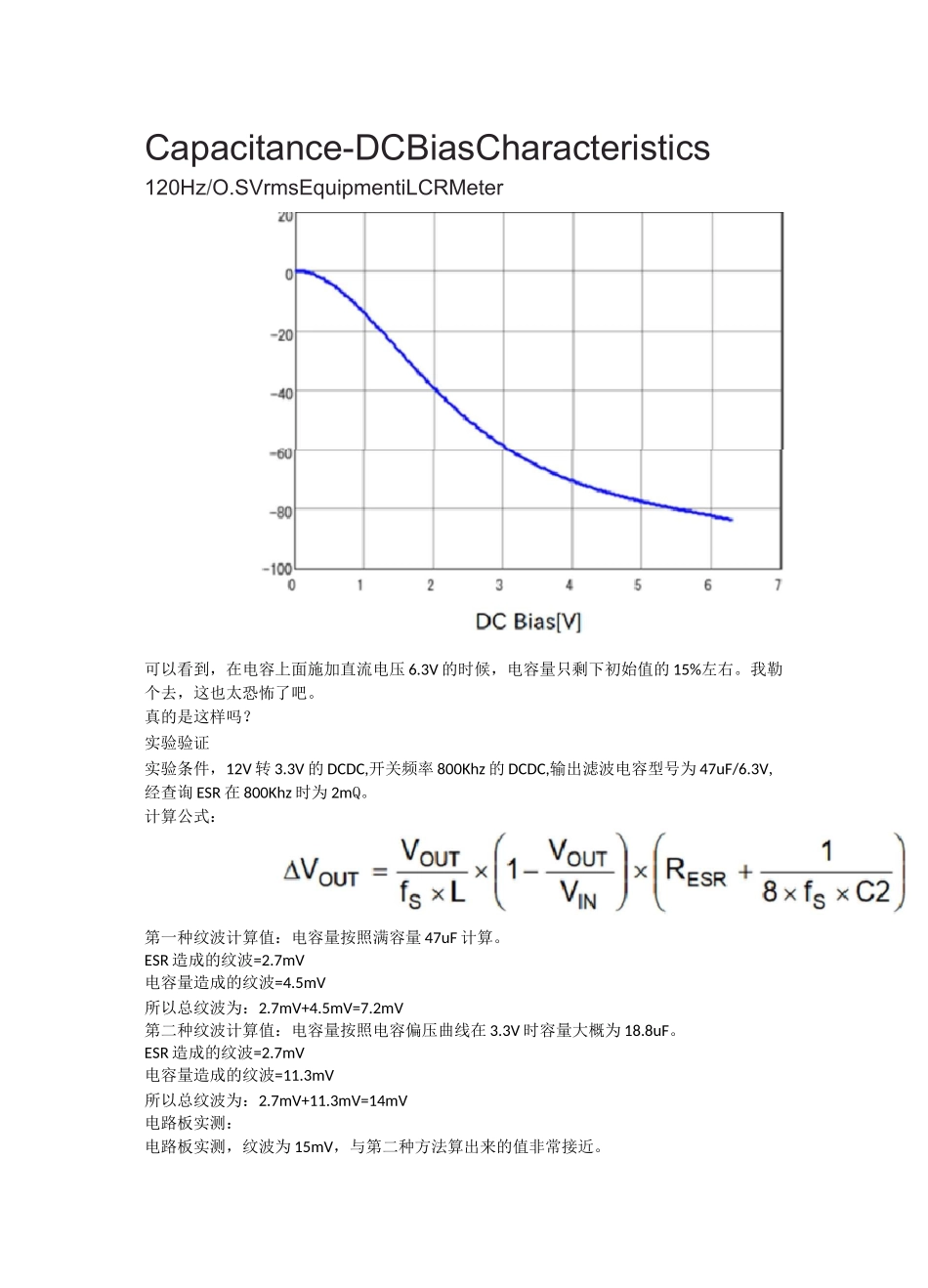

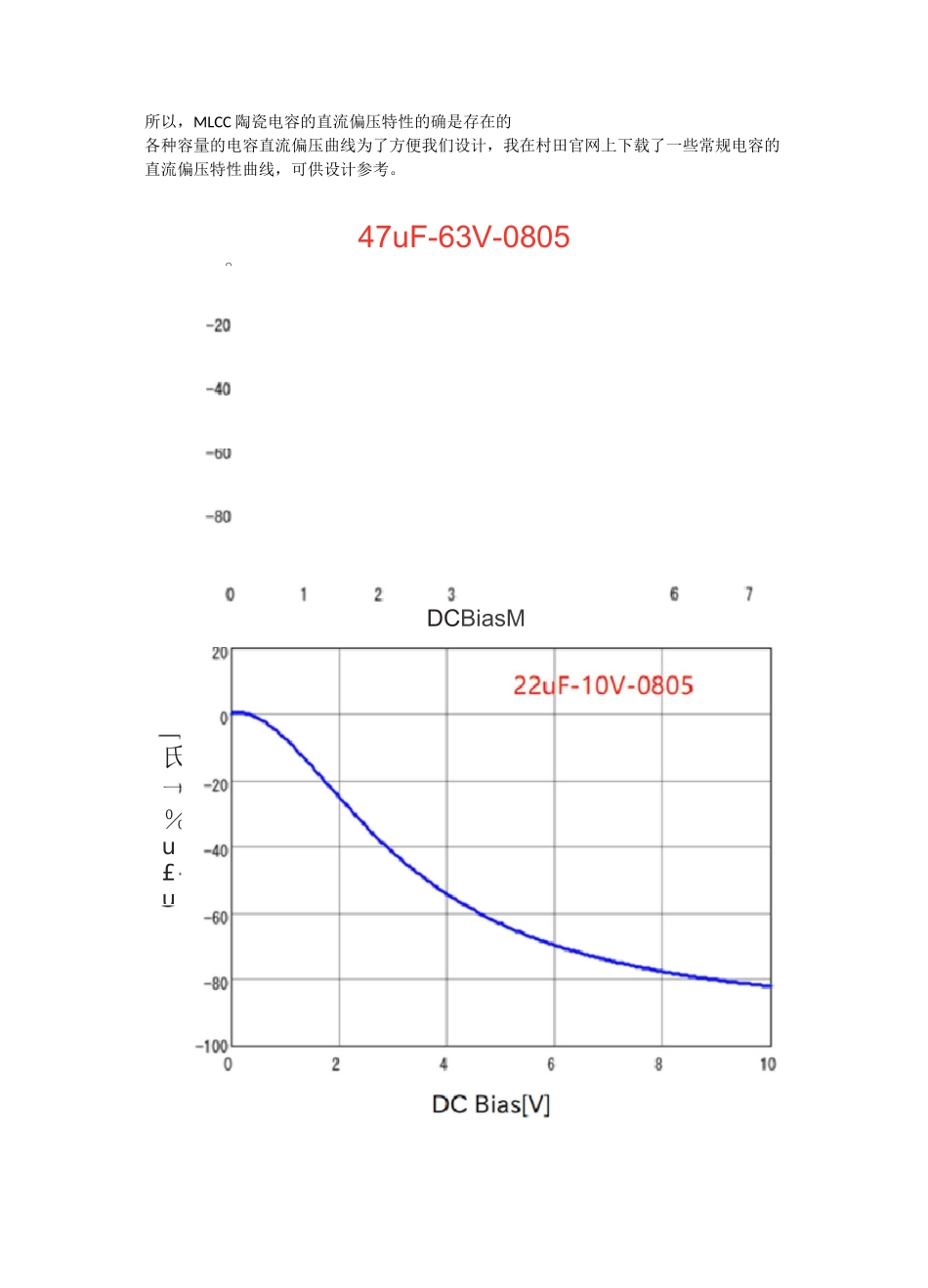

实际上是这样的,陶瓷电容MLCC有一个直流偏压特性:在电容上施加直流电压之后,电容容量会下降

电容的直流偏压特性下图是村田的47UF/6

3V电容直流偏压特性Capacitance-DCBiasCharacteristics120Hz/O

SVrmsEquipmentiLCR