南昌大学实验报告学生姓名:学号:专业班级:中兴101实验类型:■验证□综合□设计□创新实验日期:2012928实验成绩:实验一一位二进制全加器设计实验一.实验目的(1)掌握QuartusII的VHDL文本设计和原理图输入方法设计全过程;(2)熟悉简单组合电路的设计,掌握系统仿真,学会分析硬件测试结果;(3)熟悉设备和软件,掌握实验操作

二.实验内容与要求(1)在利用VHDL编辑程序实现半加器和或门,再利用原理图连接半加器和或门完成全加器的设计,熟悉层次设计概念;(2)给出此项设计的仿真波形;(3)参照实验板1K100的引脚号,选定和锁定引脚,编程下载,进行硬件测试

三.设计思路一个1位全加器可以用两个1位半加器及一个或门连接而成

而一个1位半加器可由基本门电路组成

(1)半加器设计原理能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器

或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器

图1为半加器原理图

其中:a、b分别为被加数与加数,作为电路的输入端;so为两数相加产生的本位和,它和两数相加产生的向高位的进位co一起作为电路的输出

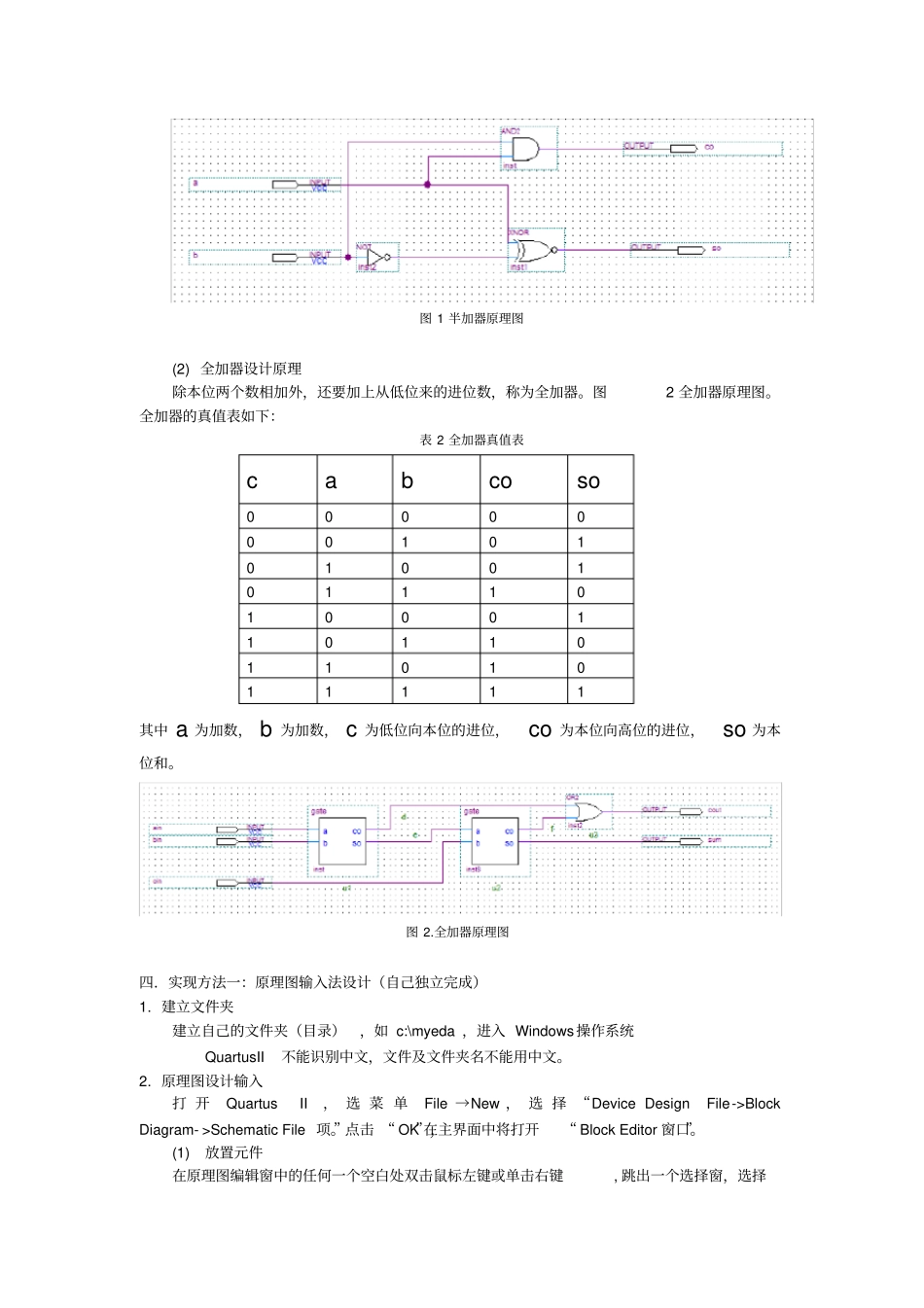

半加器的真值表为表1半加器真值表absoco0000011010101101由真值表可分别写出和数so,进位数co的逻辑函数表达式为:bababaso(1)abco(2)图1半加器原理图(2)全加器设计原理除本位两个数相加外,还要加上从低位来的进位数,称为全加器

图2全加器原理图

全加器的真值表如下:表2全加器真值表cabcoso0000000101010010111010001101101101011111其中a为加数,b为加数,c为低位向本位的进位,co为本位向高位的进位,so为本位和

全加器原理图四.实现方法一:原理图输入法设计(自己独立完成)1

建立文件夹建立自己的文件夹(目录),如c:\