目录1设计目的与作用设计目的及设计要求按要求设计三位二进制减法计数器(无效状态001,011)及用74161构成227进制同步计数器并显示,加强对数字电子技术的了解,巩固课堂上学到的知识,了解计数器,并且加强对软件multisim的了解

设计作用multisim仿真软件的使用,可以使我们对计数器及串行检测器有更深的理解,并且学会分析仿真结果,与理论结果作比较

加强了自我动手动脑的能力

2设计任务1

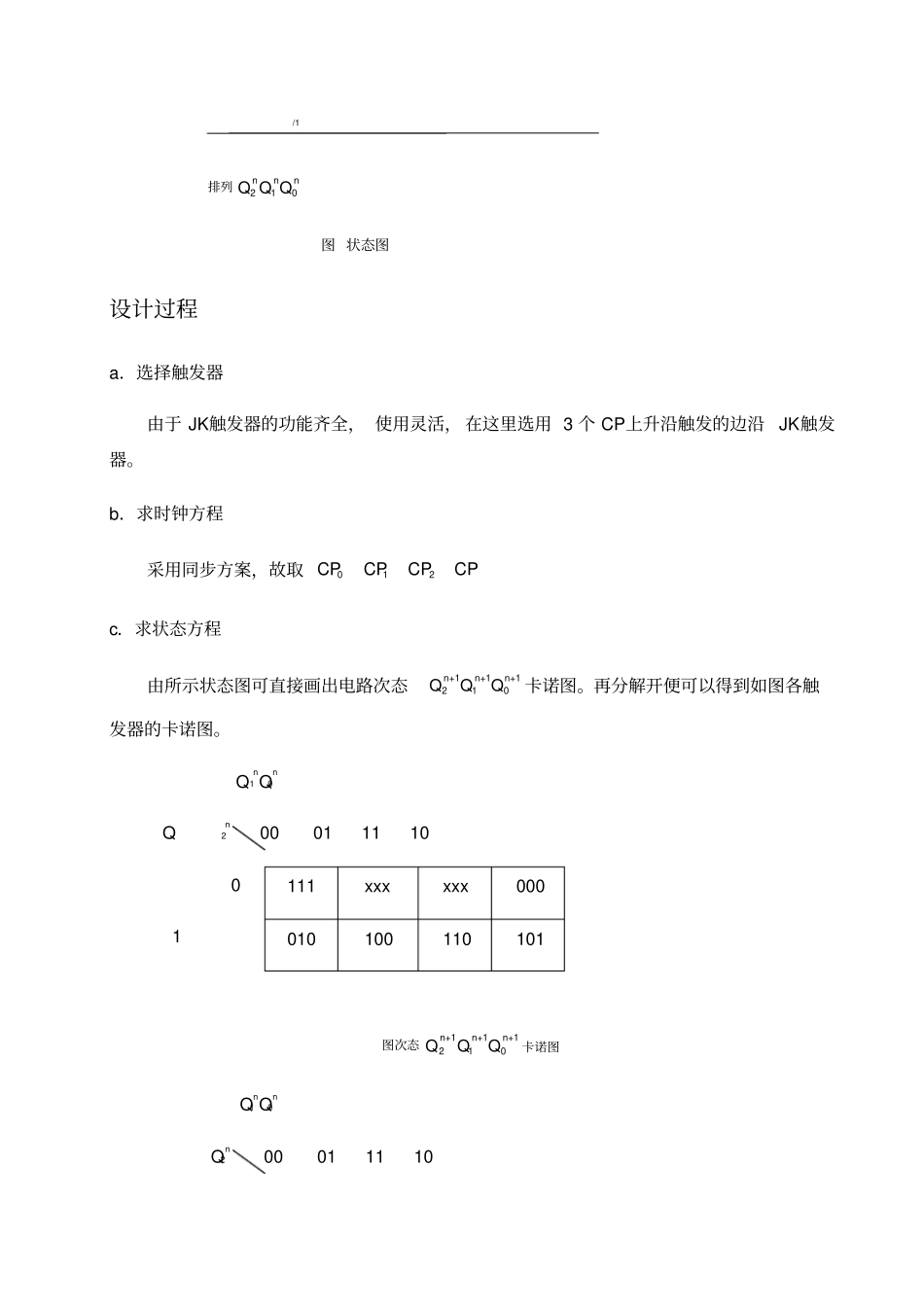

三位二进制减法计数器(无效状态001,011)构成227进制同步计数器并显示3三位二进制减法计数器的设计设计原理设计一个三位二进制减法计数器(无效状态001,011)000/0010/0100/0101/0110/0111/1排列nnn210QQQ图状态图设计过程a.选择触发器由于JK触发器的功能齐全,使用灵活,在这里选用3个CP上升沿触发的边沿JK触发器

b.求时钟方程采用同步方案,故取012CPCPCPCPc.求状态方程由所示状态图可直接画出电路次态n+1n+1n+1210QQQ卡诺图

再分解开便可以得到如图各触发器的卡诺图

Q1nQ0nQ2n0001111001图次态n+1n+1n+1210QQQ卡诺图Q1nQ0nQ2n00011110111xxxxxx00001010011010101图n+12Q的卡诺图Q1nQ0nQ2n0001111001图n+11Q的卡诺图Q1nQ0nQ2n0001111001图n+10Q的卡诺图状态方程:nnQQQQQQ01n2n1n21n2(1)nnnnnQQQQQ010111(2)1xx001111xx010101xx00001(3)(2)求驱动方程JK触发器的特性方程为nn1nQKQJQ120QQJ,nQQK1n20n011QKJn0n12QQJ,n0n12QQK(3)画逻辑电路图选用触发器,写出时钟方程,输出方程,驱动方程,便可以画出如图所