电学实验报告模板电学虚拟仿真实验室实验名称移位寄存器及其应用实验目的1

掌握中规模集成移位寄存器的逻辑功效

学习用移位寄存器构成环形计数器的办法

掌握运用中规模集成计数器设计电路的办法

实验原理移位寄存器是逻辑电路中的一种重要逻辑部件,它能存储数据,还能够用来实现数据的串行-并行转换、数据的运算和解决

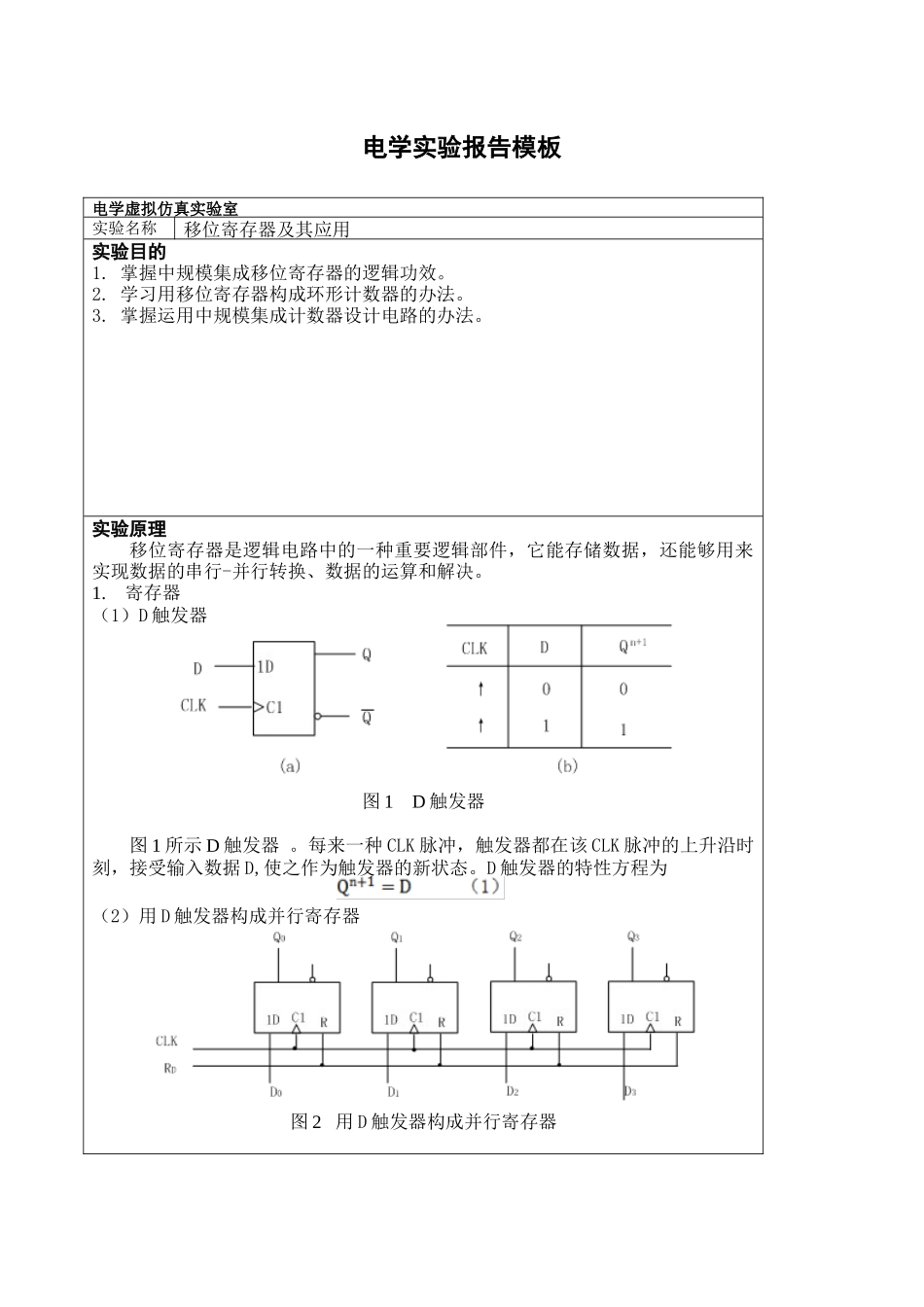

寄存器(1)D触发器图1D触发器图1所示D触发器

每来一种CLK脉冲,触发器都在该CLK脉冲的上升沿时刻,接受输入数据D,使之作为触发器的新状态

D触发器的特性方程为(2)用D触发器构成并行寄存器图2用D触发器构成并行寄存器图2所示为用D触发器构成四位并行寄存器

为异步清零控制端,高电平有效

当时,各触发器输出端Q的状态,取决于CLK上升沿时刻的D端状态

移位寄存器(1)用D触发器构成移位寄存器图3用D触发器构成4位串行移位寄存器图3所示为用D触发器构成的4位串行移位寄存器

其中左边第一种触发器的输入端接受输入数据,其它的每一种触发器的输入端均与左边相邻的触发器的Q端连接

当时钟信号CLK的上升沿时刻,各触发器同时接受输入数据

四位寄存器的所存数据右移一位

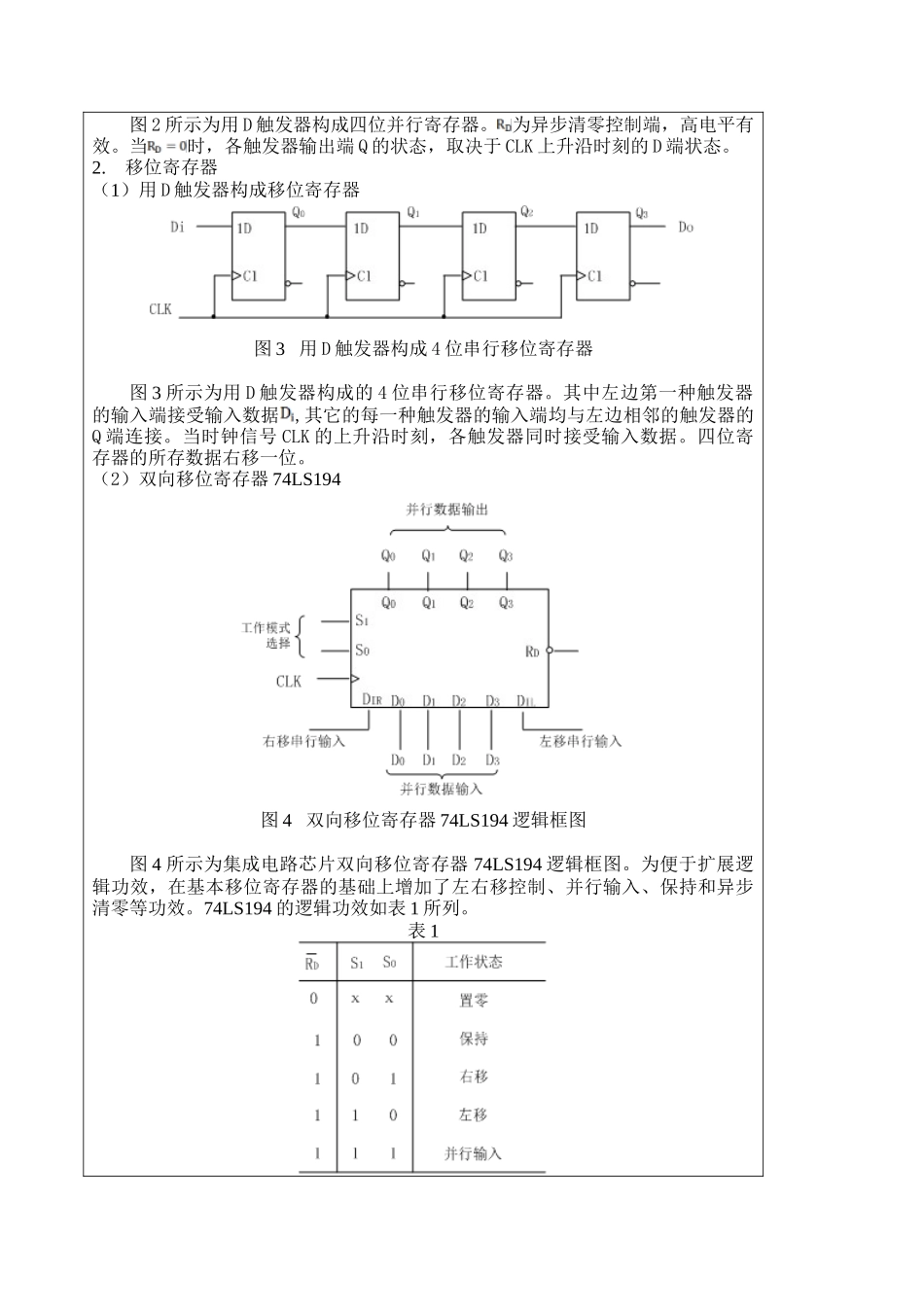

(2)双向移位寄存器74LS194图4双向移位寄存器74LS194逻辑框图图4所示为集成电路芯片双向移位寄存器74LS194逻辑框图

为便于扩展逻辑功效,在基本移位寄存器的基础上增加了左右移控制、并行输入、保持和异步清零等功效

74LS194的逻辑功效如表1所列

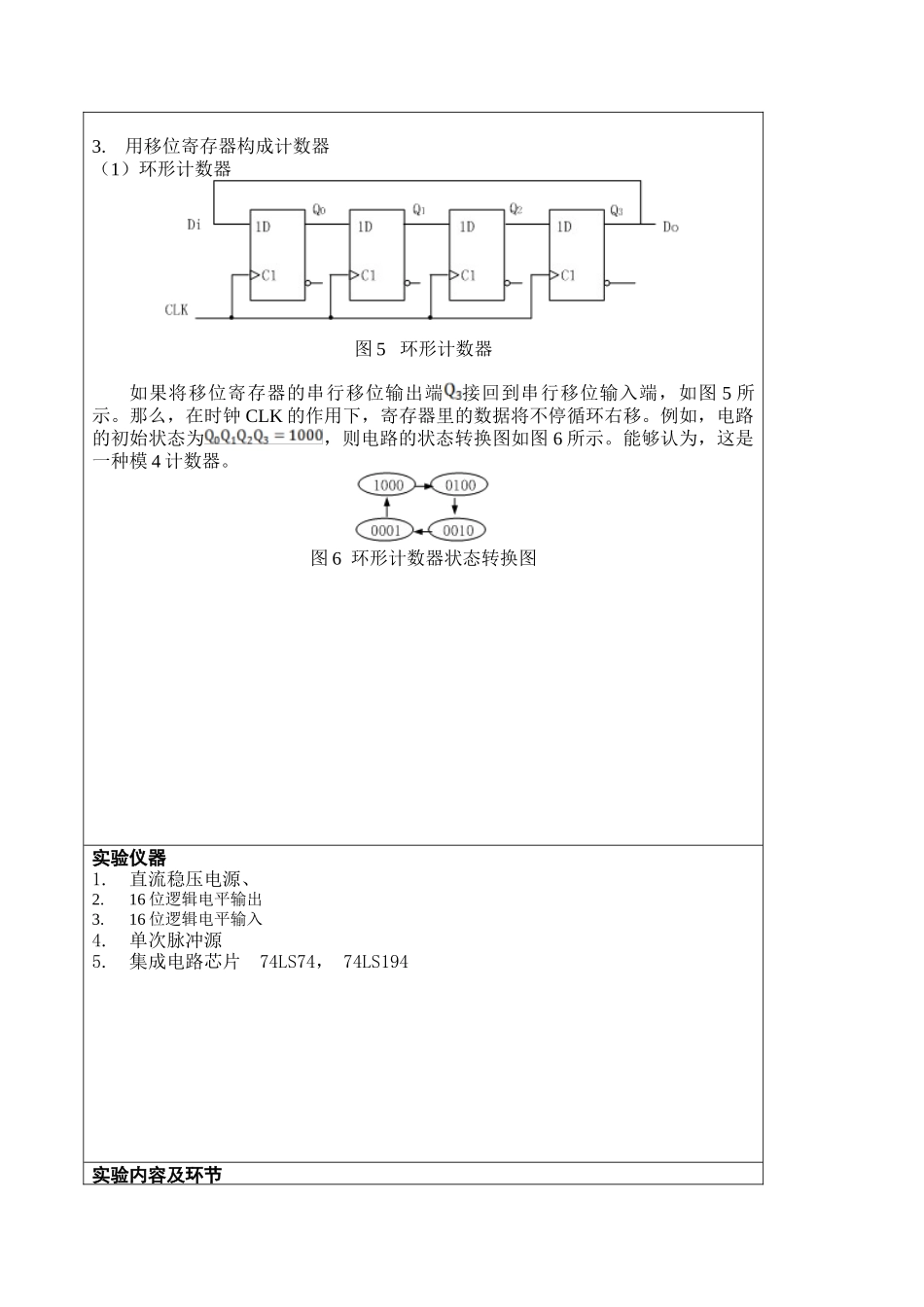

用移位寄存器构成计数器(1)环形计数器图5环形计数器如果将移位寄存器的串行移位输出端接回到串行移位输入端,如图5所示

那么,在时钟CLK的作用下,寄存器里的数据将不停循环右移

例如,电路的初始状态为,则电路的状态转换图如图6所示

能够认为,这是一种模4计数器

图6环形计数器状态转换图实验仪器1

直流稳压电源、2

16位逻辑电平输出3