CSP 装配的可靠性本文对三种芯片规模包装及其装配的可靠性进行比较

板面焊接点可靠性信息的获得对于芯片规模包装(CSP, chip-scale backage)的广泛实施是关键的

本文比较三个不同的 CSP 概念及其装配的可靠性

另外,将使用一个修饰的 Coffin-Manson 关系,对一个专门的温度循环范围,设计出有关几种低输入/输出(I/O)包装的焊接点可靠性的循环数据文献

由喷气推进实验室(JPL, Jet Propulsion Laboratory, Pasadena, CA)组织了一个微型 BGA 协会,来探讨有关包装类型、I/O 数、PWB 材料与类型和制造变量对品质和电路板可靠性的相互作用的技术问题

这里呈现给大家的是来自这个课题的最新结果

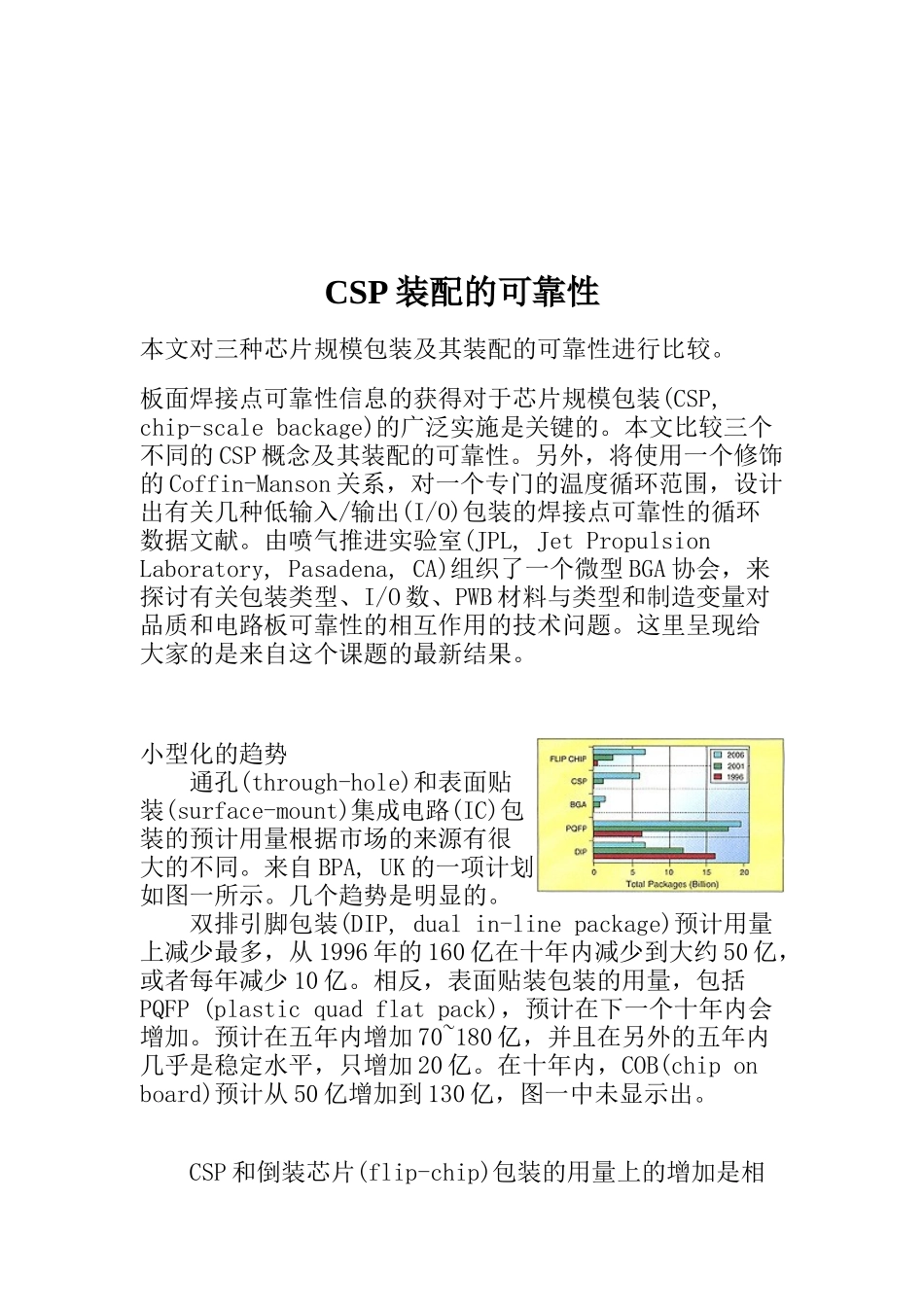

小型化的趋势 通孔(through-hole)和表面贴装(surface-mount)集成电路(IC)包装的预计用量根据市场的来源有很大的不同

来自 BPA, UK 的一项计划如图一所示

几个趋势是明显的

双排引脚包装(DIP, dual in-line package)预计用量上减少最多,从 1996 年的 160 亿在十年内减少到大约 50 亿,或者每年减少 10 亿

相反,表面贴装包装的用量,包括PQFP (plastic quad flat pack),预计在下一个十年内会增加

预计在五年内增加 70~180 亿,并且在另外的五年内几乎是稳定水平,只增加 20 亿

在十年内,COB(chip on board)预计从 50 亿增加到 130 亿,图一中未显示出

CSP 和倒装芯片(flip-chip)包装的用量上的增加是相同的

预计在 2006 年达到 60 亿

相反,在相同十年里 BGA的增加预计是最小的,达到只有 15 亿的总用量

对 BGA 的预计表明也许这些包装只是一个踏步石,工业将更广泛地接受倒装芯