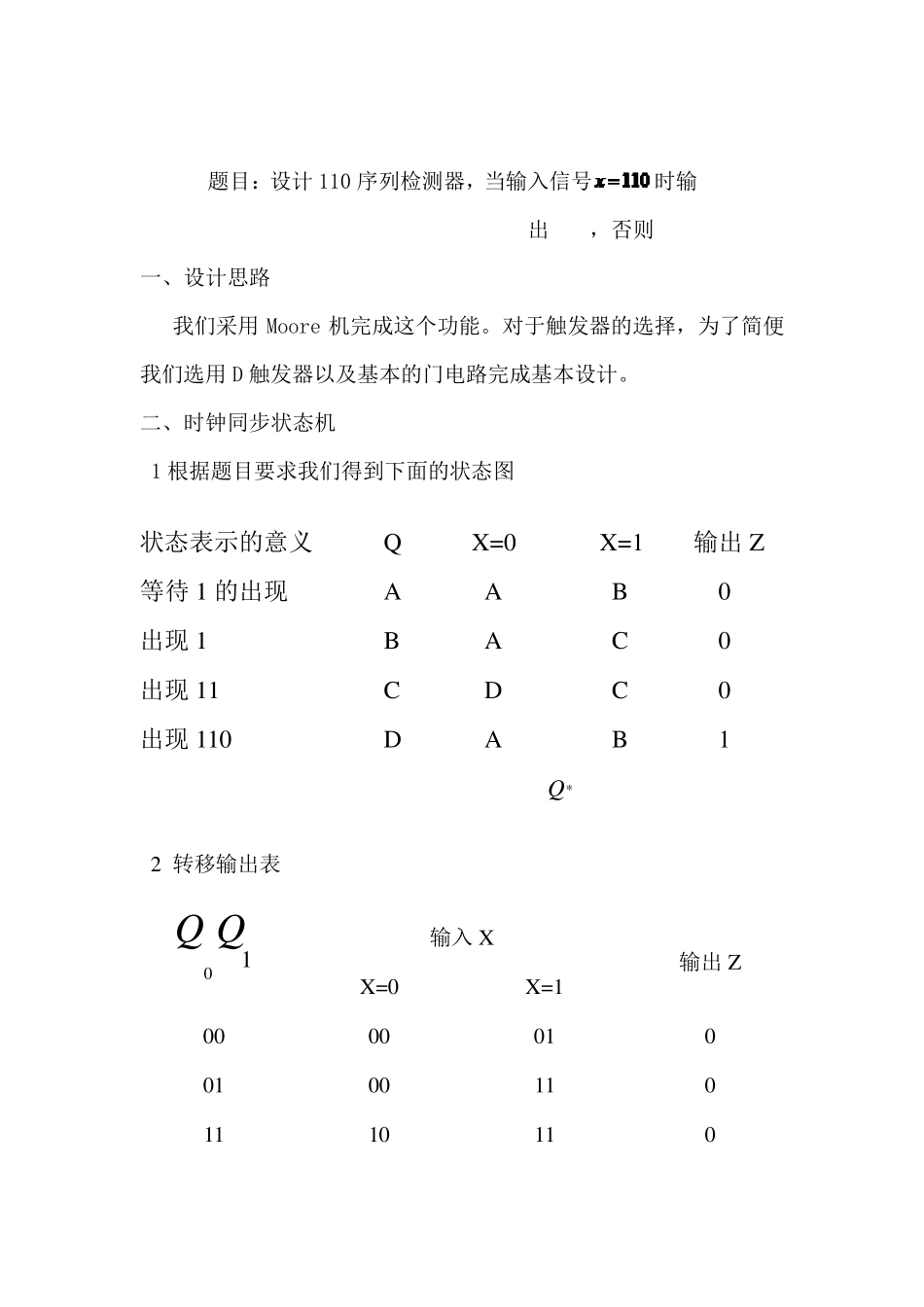

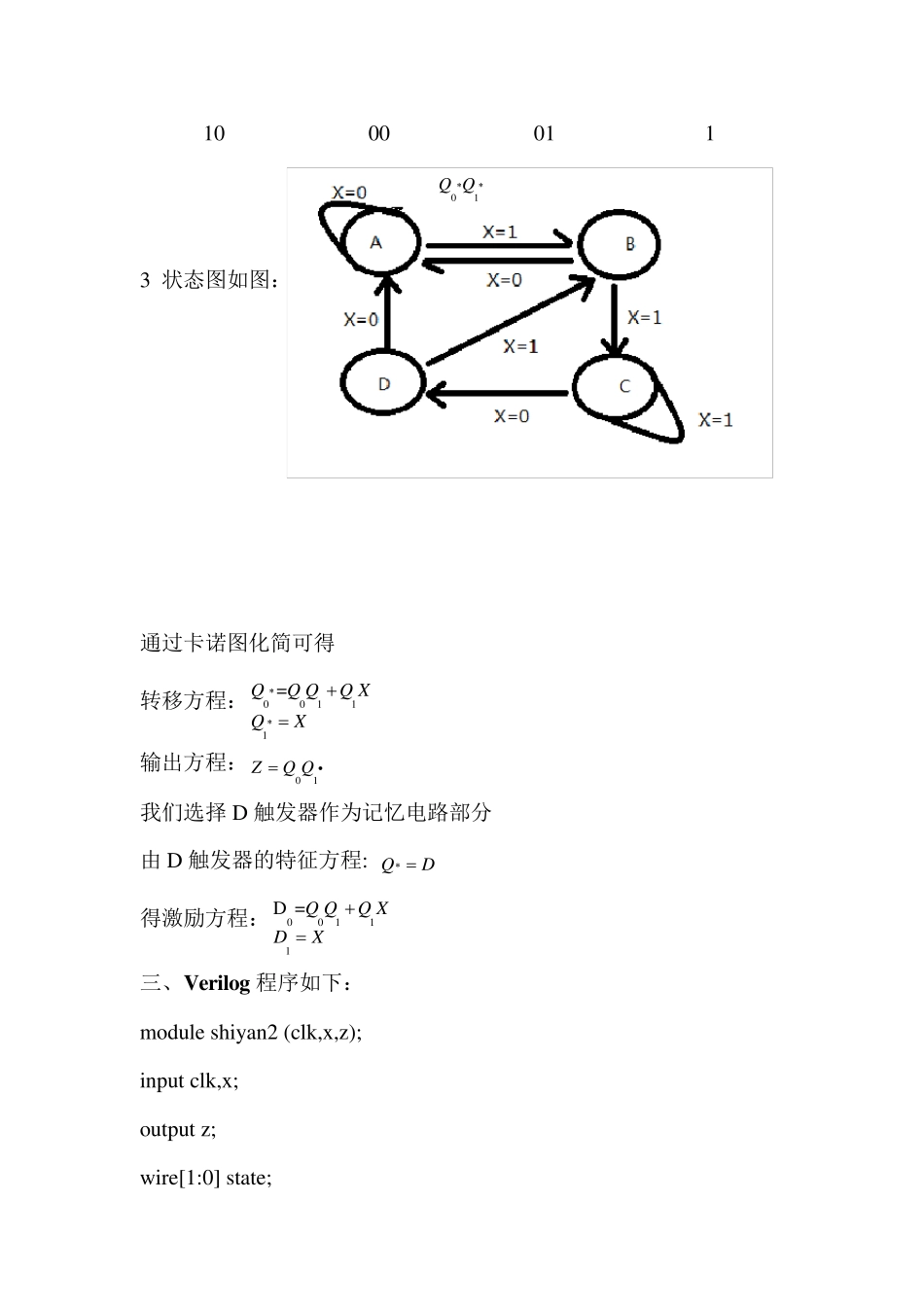

题目:设计110 序列检测器,当输入信号时输出,否则 一、设计思路 我们采用 Moore 机完成这个功能。对于触发器的选择,为了简便我们选用 D 触发器以及基本的门电路完成基本设计。 二、时钟同步状态机 1 根据题目要求我们得到下面的状态图 状态表示的意义 Q X=0 X=1 输出Z 等待 1 的出现 A A B 0 出现 1 B A C 0 出现 11 C D C 0 出现 110 D A B 1 *Q 2 转移输出表 01Q Q 输入X 输出Z X=0 X=1 00 00 01 0 01 00 11 0 11 10 11 0 10 00 01 1 01Q Q 3 状态图如图: 通过卡诺图化简可得 转移方程:00111=QQ QQ XQX 输出方程:01ZQ Q • 我们选择D 触发器作为记忆电路部分 由D 触发器的特征方程: QD 得激励方程:00111D =Q QQ XDX 三、Verilog 程序如下: module shiyan2 (clk,x,z); input clk,x; output z; wire[1:0] state; wire[1:0] excite; nextlogic u1(x,state,excite); statememory u2(clk,excite,state); outputlogic u3(state,z); endmodule module statememory (clk,d,q); input clk; input[1:0] d; output[1:0] q; reg[1:0] q; always @ (posedge clk) begin q <= d; end endmodule module nextlogic (x,q,d); input x; input[1:0] q; output[1:0] d; assign d[0]=(q[1]&q[0])|(q[1]&x); assign d[1]=x; endmodule module outputlogic (q,z); input[1:0] q; output z; assign z=(!q[1])&q[0]; Endmodule 四、仿真结果及电路图 得到功能仿真结果为: 时序仿真结果为: 利用程序生成的电路图为 从电路图和仿真结果来看这次的仿真能够完全达到题目的要求。