NiosII 软件设计与运行流程 本实验是于实验1 相连的,本实验主要完成在NiosII 硬件系统完成及下载于FPGA 中的基础上,进行软件开发、下载和调试,具体流程如下: 1、 向FPGA 下载配置文件

以下的实验将更多地与SOPC 实验系统联系

本次实验是使用清华大学电工电子实验中心的GW48-SOPC 实验系统(康芯公司),下载前连接好下载通信线,打开电源,打开光盘上关于此实验系统的PDF/PPT 默认设置说明,确认实验系统所有开关和跳线处于默认设置位置

用 10 芯通信线将实验系统左侧的“Byterblaster II”接口与适配板上的JTAG Port 口相连; 将实验系统左侧的跳线短路帽接插“ByBt II”端,编程电压选择跳线短路帽插3

3V(此电压接错不会损坏系统)

按动实验系统左下角的电路模式控制键,选择模式5(在上方的数码管会显示5 字) ,这时实验系统将进入附录中附图1 的电路连接模式(有12 中不同的可选硬件电路模式)

注意模式5 的 8 个键控特点:每按键一次,输出电平反相一次,电平高低由此键上方的发光管显示; 还注意到此时FPGA 输出的32 个 I/O 口接了8 个数码管,每 4 个 I/O 口接一个数码管,且在每一数码管外接了一个16 进制至7 段译码的译码器,这样可以大大节省I/O 口的耗用

FPGA 的主要端口是用标准信号名PIOx标注的,具体引脚号在引脚锁定时查阅附录的附表1;例如附图1 中连接FPGA 的键8 端口标准信号名是“PIO7”,查附表1,横项GW48-SOPC 对应Pin240

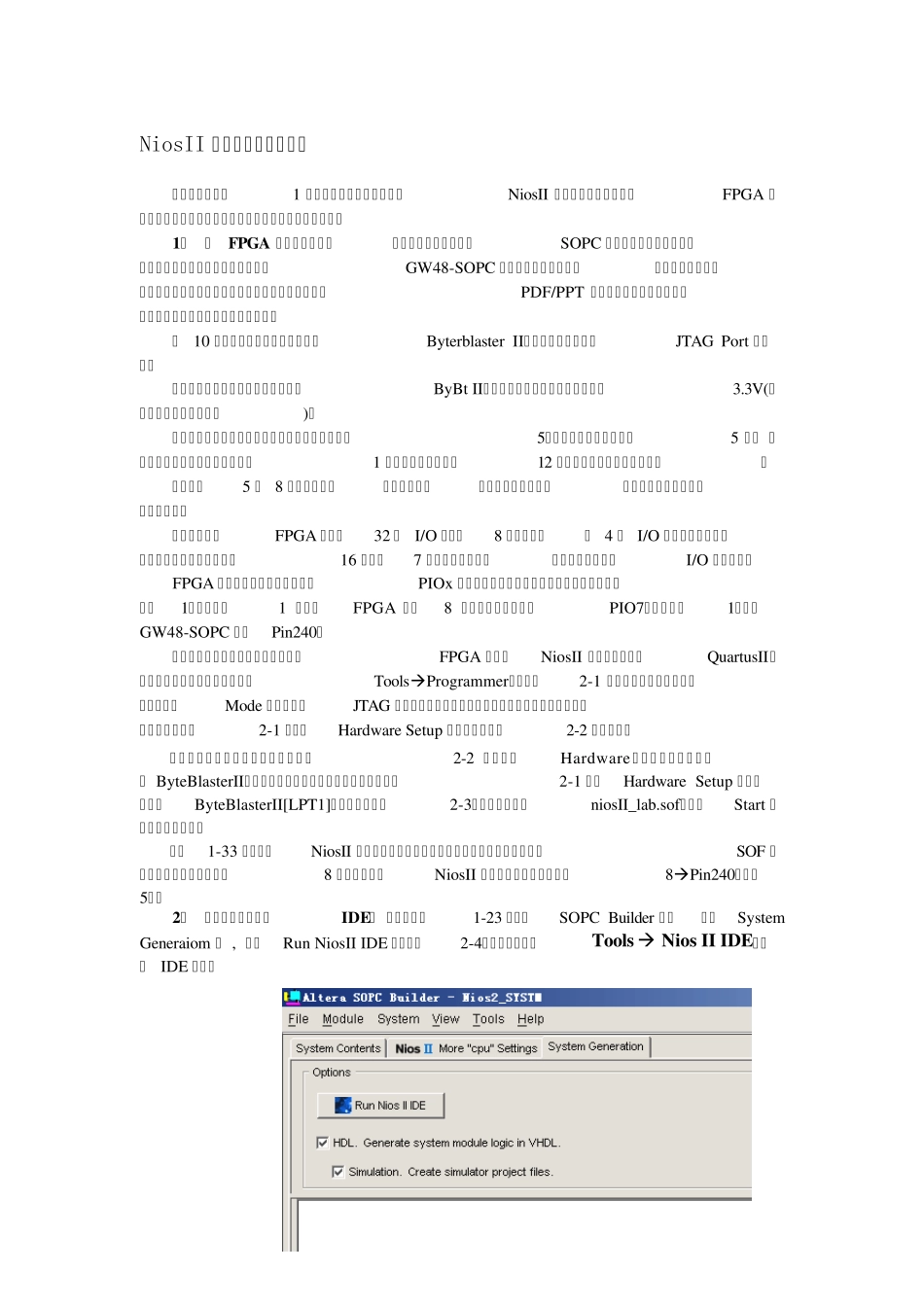

现在可以开始下载配置文件,以便在FPGA 中建立NiosII 硬件环境

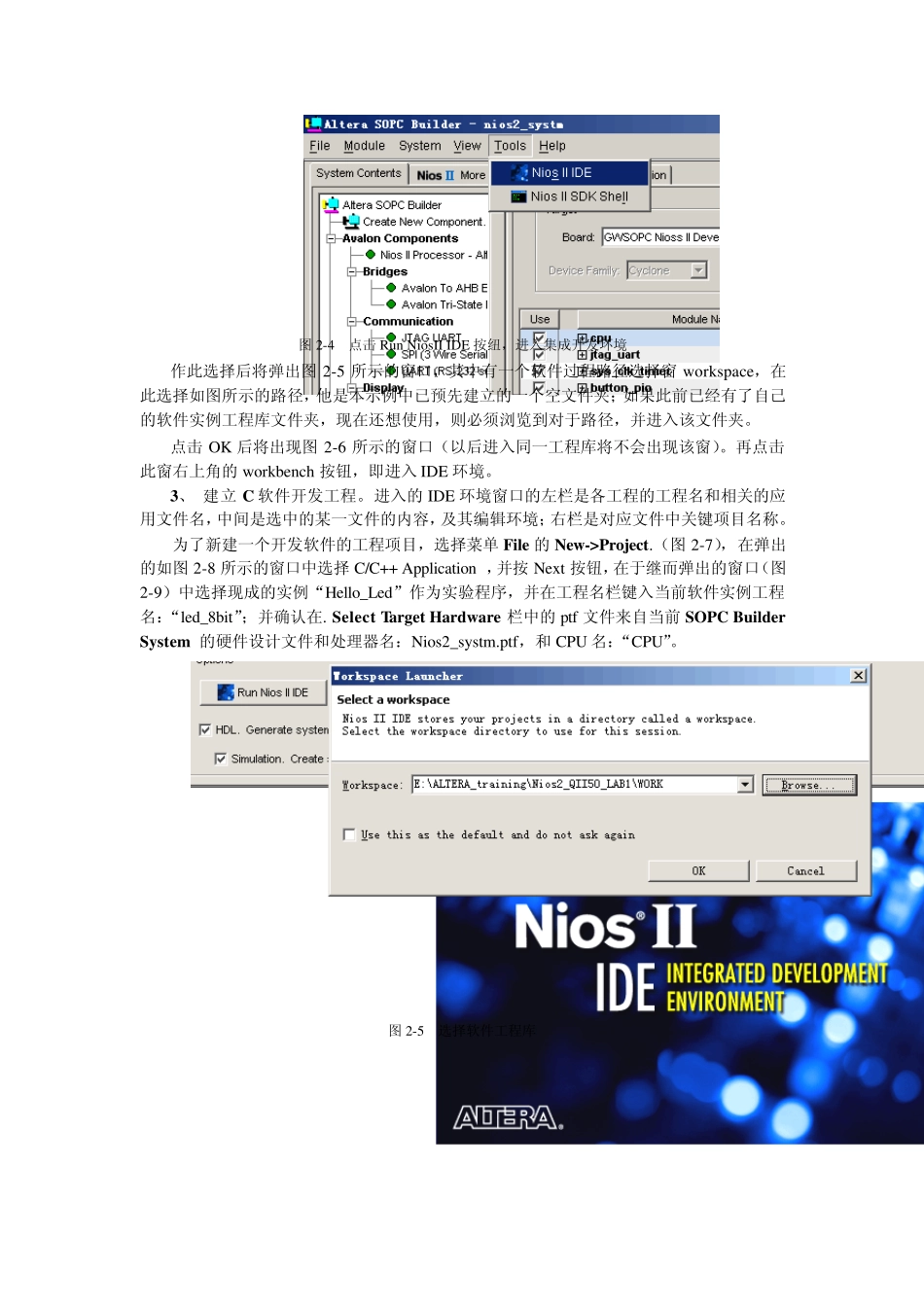

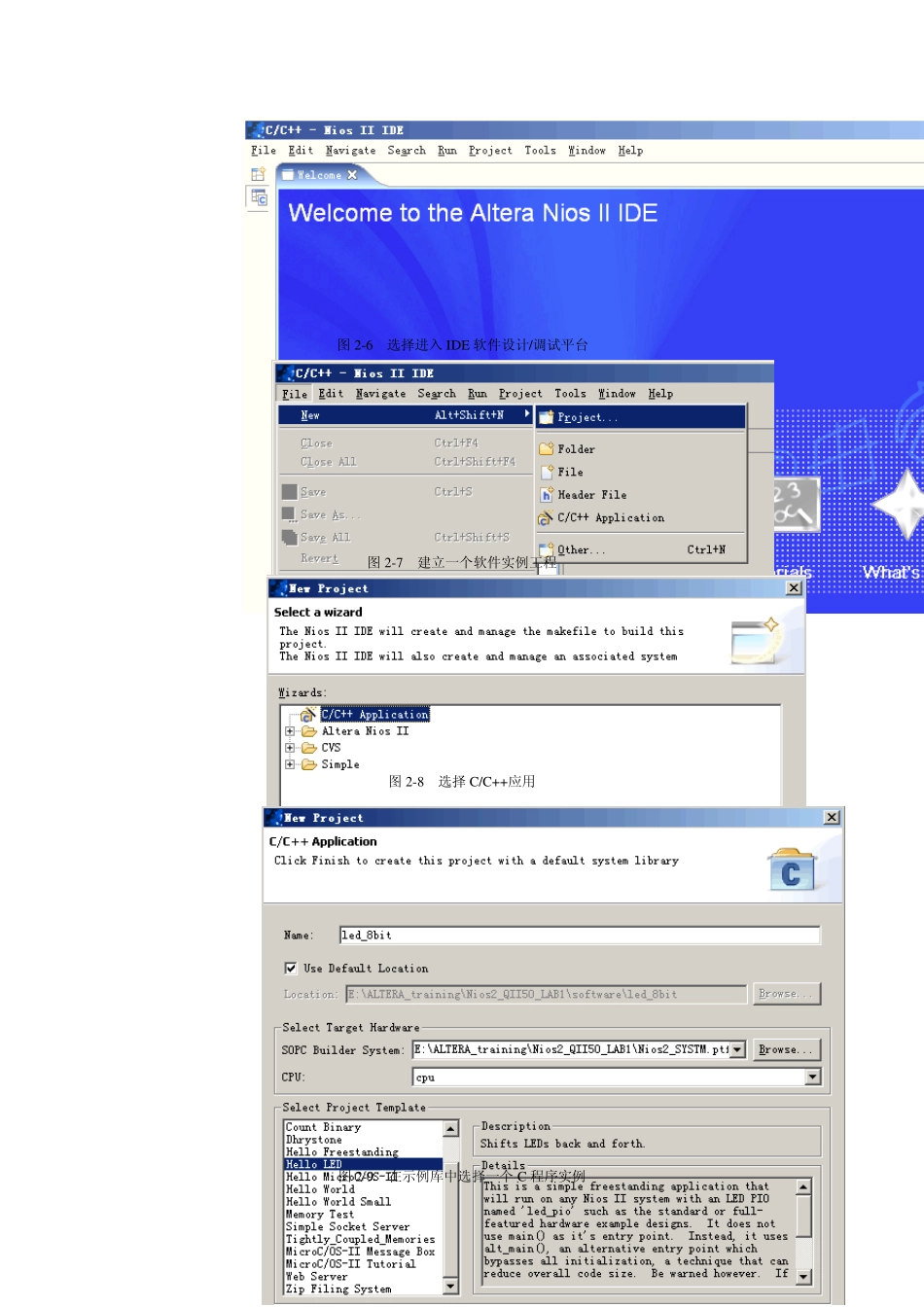

打开QuartusII,再打开实验一的工程,选择菜单ToolsProgrammer,弹出图2-1 所示窗口,首先选择接口模式,对于Mode 栏确认选择JTAG 模式