用quartus II 软件设计4 位乘法器 1

并行乘法的算法: 下面根据乘法例题来分析这种算法,题中M4,M3,M2,M1是被乘数,用M 表示

N4,N3,N2,N1 是乘数,用N 表示 2

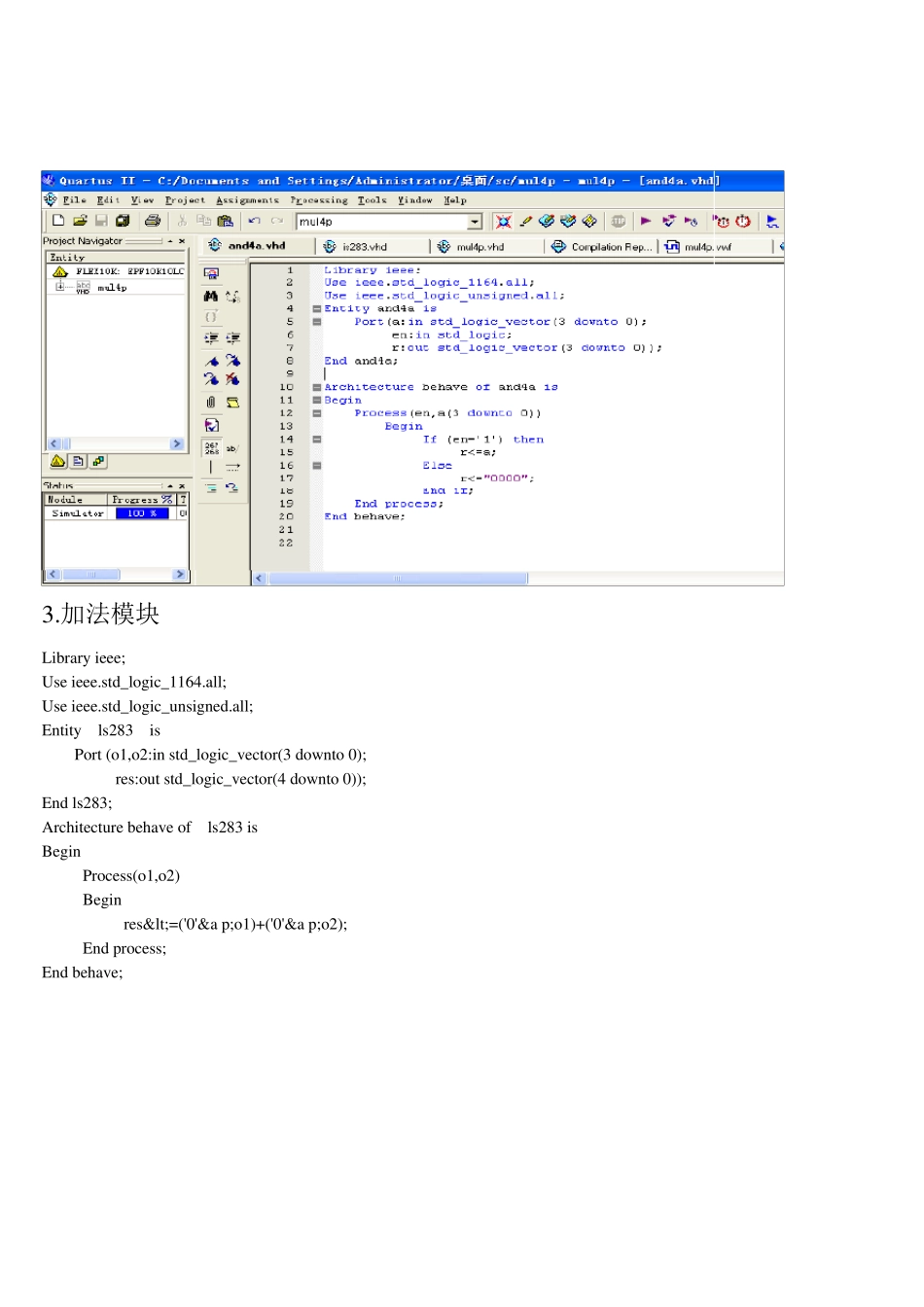

乘法模块 Library ieee; Use ieee

std_logic_1164

all; Use ieee

std_logic_unsigned

all; Entity and4a is Port(a:in std_logic_vector(3 downto 0); en:in std_logic; r:out std_logic_vector(3 downto 0)); End and4a; Architecture behave of and4a is Begin Process(en,a(3 downto 0)) Begin If (en='1') then rop1(3),r=>sa); U2:ls283 port map(o1=>sb(4 dow nto 1),o2=>sa,res=>result(7 dow nto 3)); U3:and4a port map(a=>op2,en=>op1(2),r=>sc); U4:ls283 port map(o1=>sc,o2=>sd(4 dow nto 1),res=>sb); u5:ls283 port map(o1=>sg,o2=>se,res=>sd); u6:and4a port map(a=>op2,en=>op1(0),r=>sf); result(0)