随着FPGA 设计任务复杂性的不断提高,FPGA 设计调试工作的难度也越来越大,在设计验证中投入的时间和花费也会不断增加

为了让产品更快投入市场,设计者必须尽可能减少设计验证时间,这就需要一套功能强大且容易使用的验证工具

Altera SignalTap Ⅱ逻辑分析仪可以用来对 Altera FPGA 内部信号状态进行评估,帮助设计者很快发现设计中存在问题的原因

Quartus Ⅱ软件中的SignalTap Ⅱ逻辑分析仪是非插入式的,可升级,易于操作且对Quartus Ⅱ用户**

SignalTap Ⅱ逻辑分析仪允许设计者在设计中用探针的方式探查内部信号状态,帮助设计者调试FPGA 设计

SignalTap Ⅱ逻辑分析仪支持下面的器件系列:Stratix Ⅱ、Stratix、Stratix GX、Cyclone Ⅱ、Cyclone、APEX Ⅱ、APEX 20KE、APEX 20KC、APEX 20K、Excalibur和Mercury

1 在设计中嵌入SignalTap Ⅱ逻辑分析仪 在设计中嵌入SignalTap Ⅱ逻辑分析仪有两种方法:第一种方法是建立一个 SignalTap Ⅱ文件(

stp),然后定义 STP 文件的详细内容;第二种方法是用MegaWizard Plug-InManager 建立并配置 STP 文件,然后用MegaWizard 实例化一个 HDL 输出模块

1 给出用这两种方法建立和使用SignalTap Ⅱ逻辑分析仪的过程

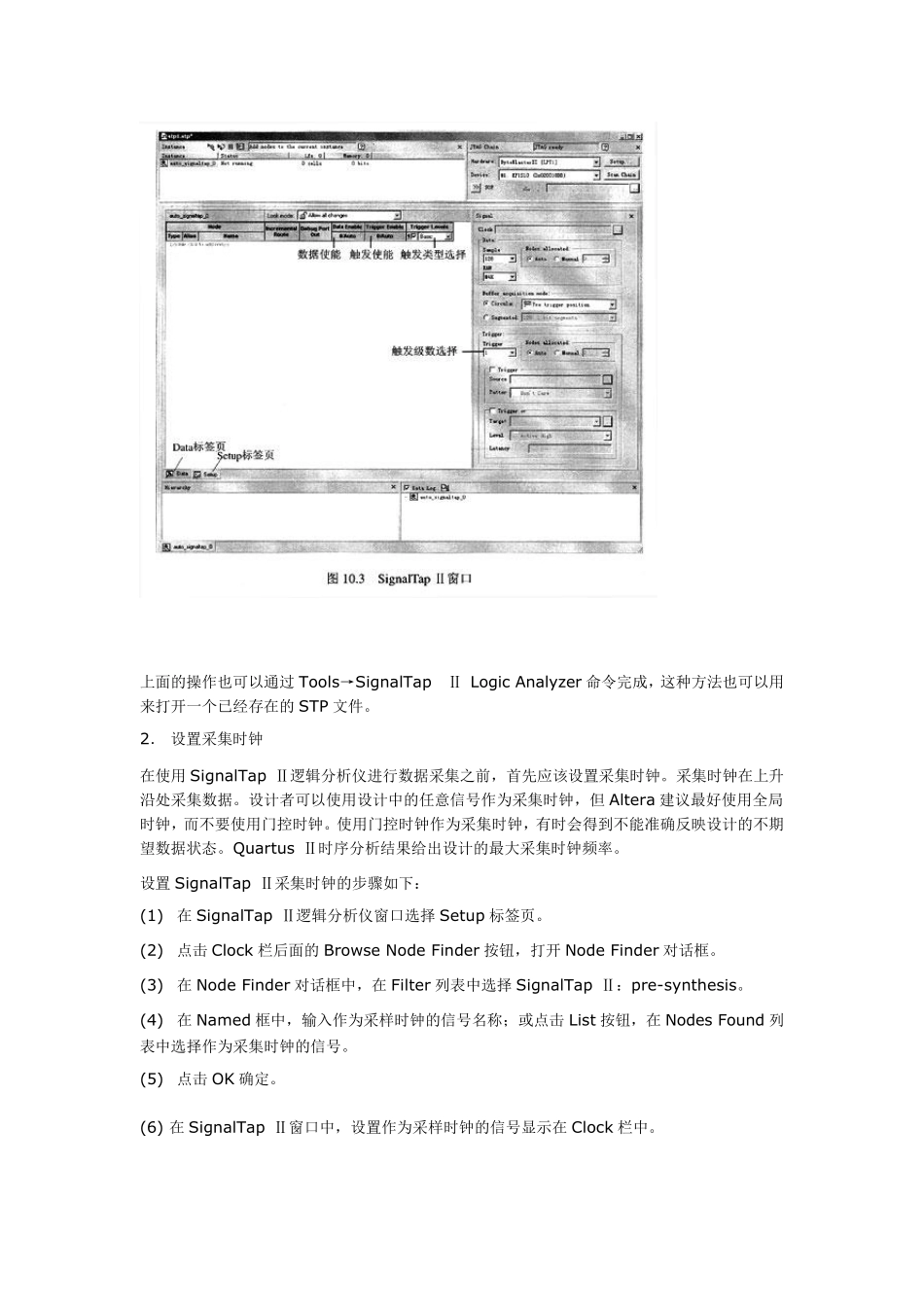

1 使用STP 文件建立嵌入式逻辑分析仪 1. 创建 STP 文件 STP 文件包括 SignalTap Ⅱ逻辑分析仪设置部分和捕获数据的查看、分析部分

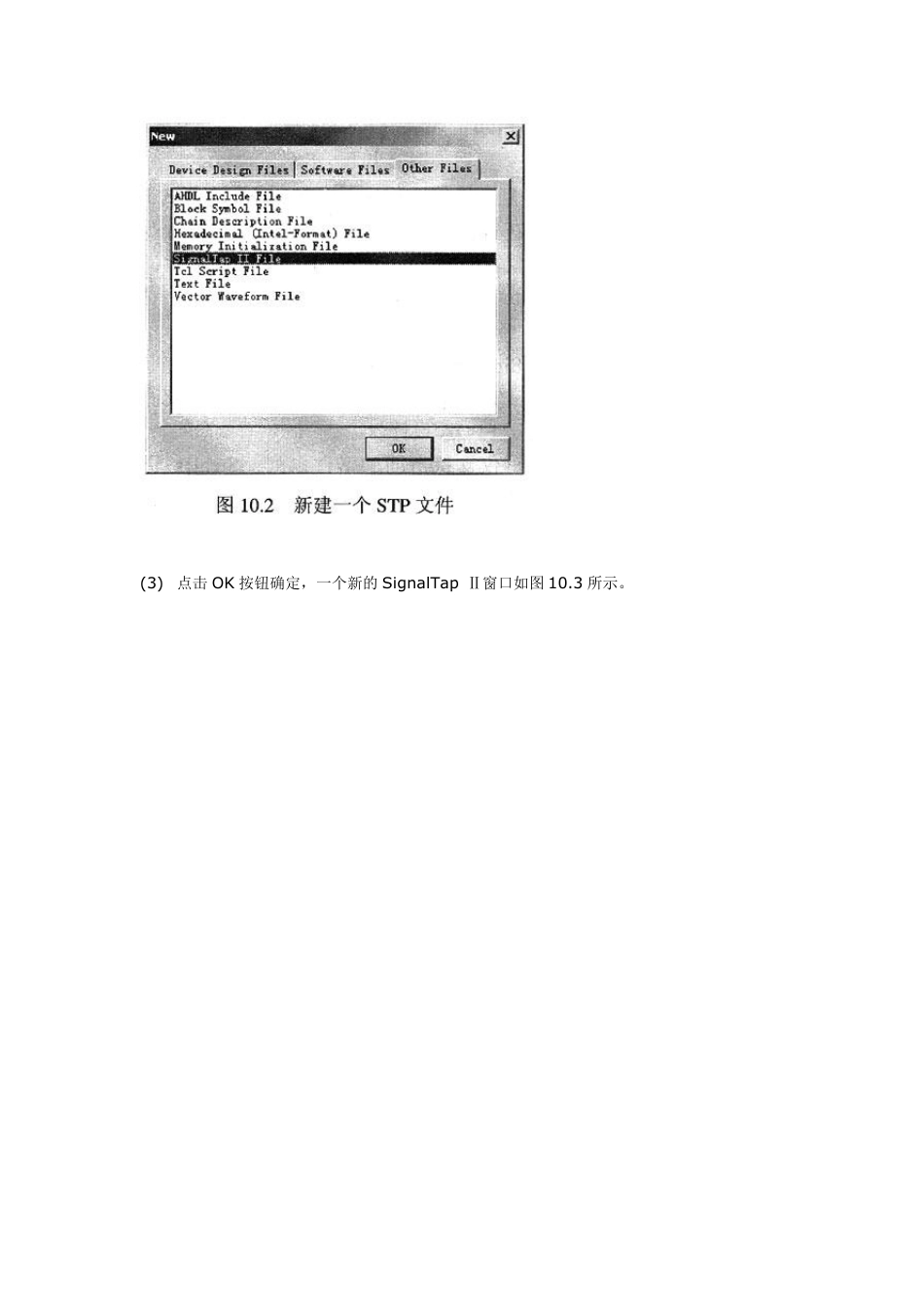

创建一个 STP文件的步骤如下: (1) 在Quartus Ⅱ软件中,选择 File→New 命令

(2) 在弹出的New 对话框中,选择