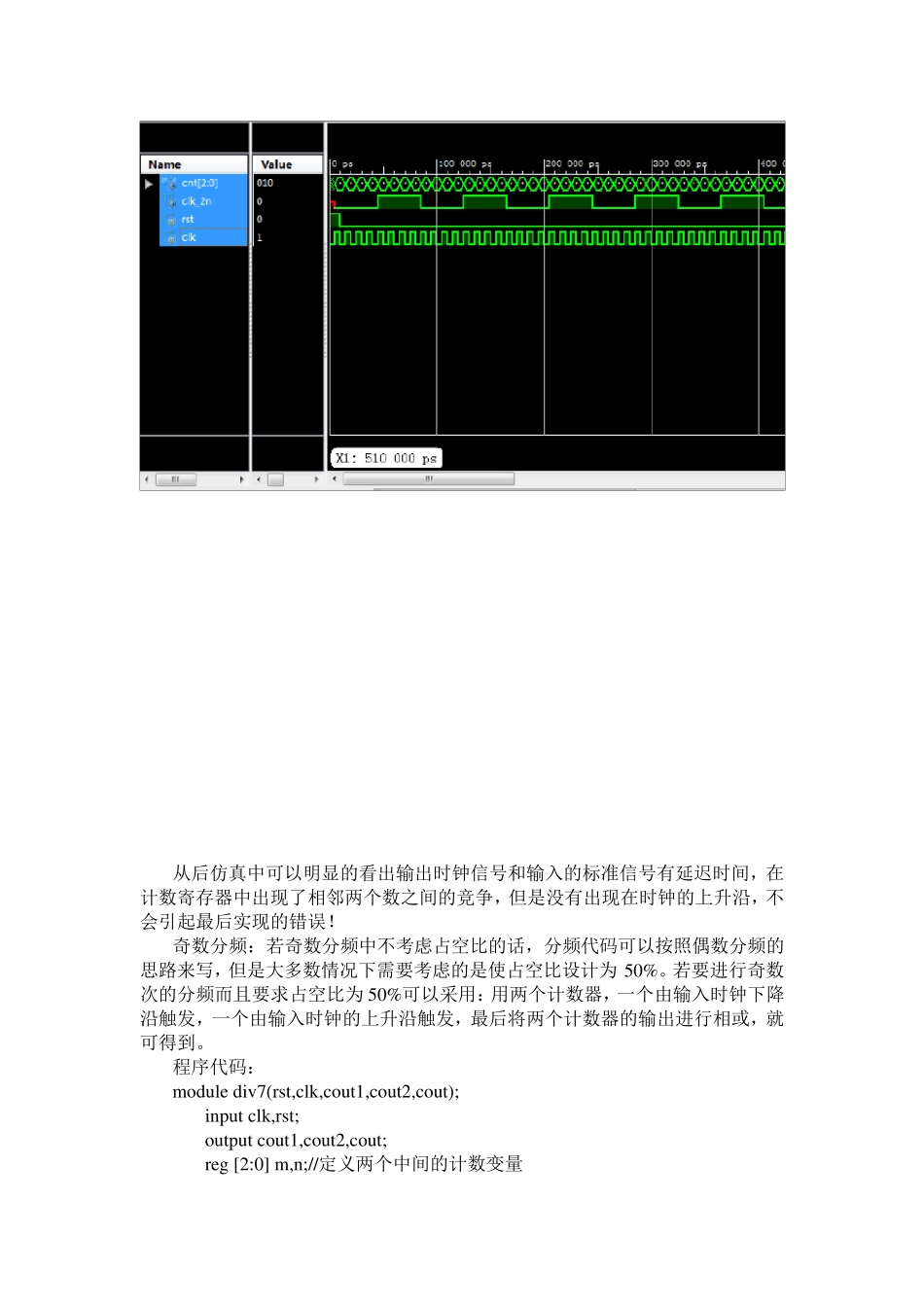

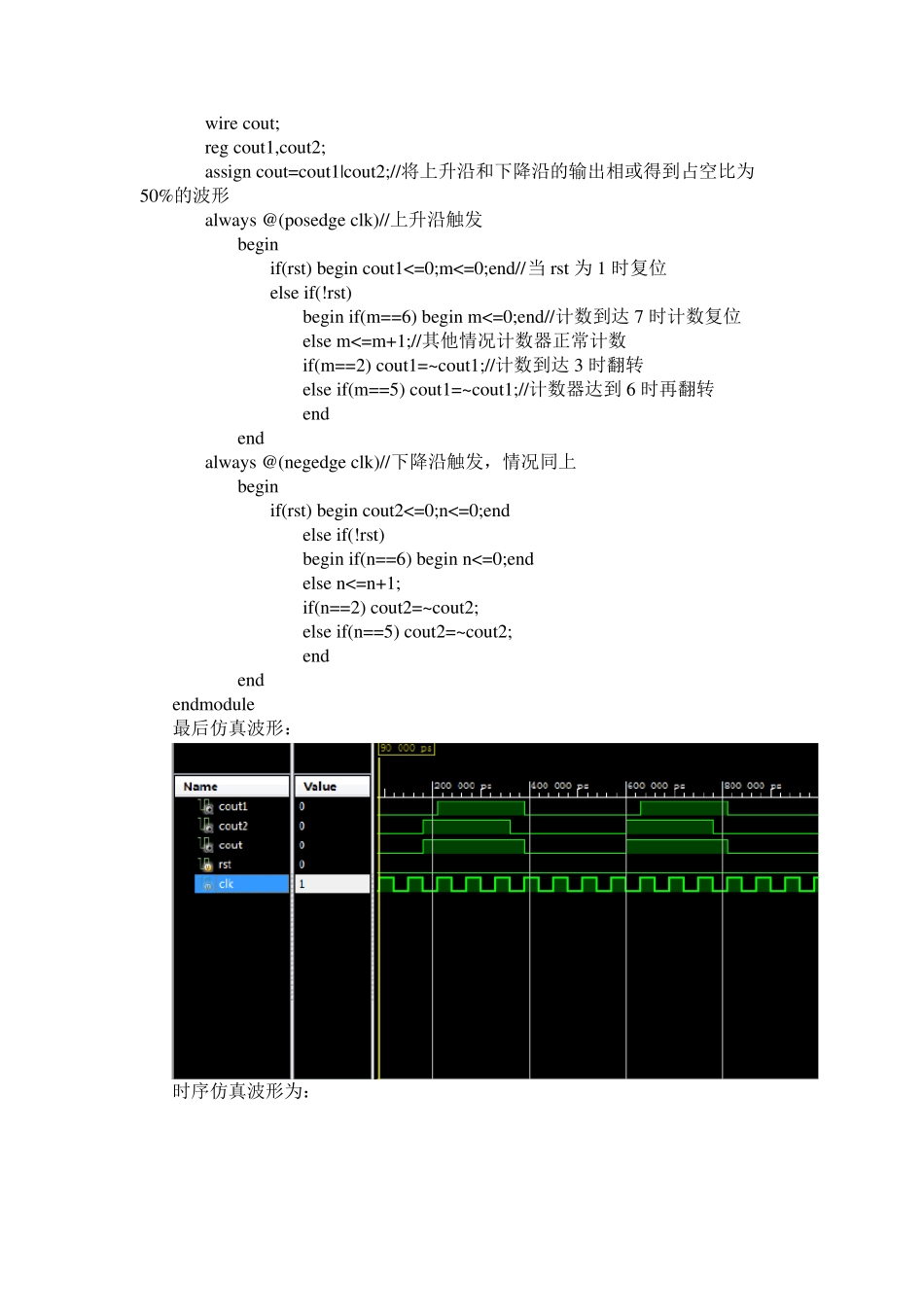

分频的Verilog 实现 1. 分频:在实际应用中,自己设计的开发板上不会去装多个晶振来产生不同频率的时钟信号,这就要我们在已有的基础上自己来创造设计电路中所需要的时钟信号来,有时候所需要的频率并不是在已有的频率上直接进行简单的整数分频就可以得到的,有时需要进行小数的分频。 2. 在分频的过程中,偶数分频并不困难,若要进行2N 次分频的话,只需要计数到N 的时候,波形进行翻转就行了,或者在最后一级加一个2分频也可以实现。 下面是我写的一个偶数分频的代码: module div2n(rst,clk,cnt,clk_2n);//偶数次分频 input rst,clk; output clk_2n,cnt; reg [3:0] cnt;//刚开始没有定义计数的位宽仿真的时候老是出现输出为 0 的现象,看似很简单的程序搞的有些纠结啊 reg clk_2n; always @(posedge clk ) begin if(rst) //若复位信号为高电平则计数清零和输出清零 begin cnt<=0; clk_2n<=0; end else if(cnt==3)//进行8 分频,这里的cnt 取不同的值进行其他的分频,若计数到达 4 时从 0 开始的输出电平翻转 begin clk_2n<=~clk_2n; cnt<=0; end else cnt<=cnt+1; end endmodule 功能仿真波形以及后仿真波形如下: 从后仿真中可以明显的看出输出时钟信号和输入的标准信号有延迟时间,在计数寄存器中出现了相邻两个数之间的竞争,但是没有出现在时钟的上升沿,不会引起最后实现的错误! 奇数分频:若奇数分频中不考虑占空比的话,分频代码可以按照偶数分频的思路来写,但是大多数情况下需要考虑的是使占空比设计为50%。若要进行奇数次的分频而且要求占空比为50%可以采用:用两个计数器,一个由输入时钟下降沿触发,一个由输入时钟的上升沿触发,最后将两个计数器的输出进行相或,就可得到。 程序代码: modu le div 7(rst,clk,cou t1,cou t2,cou t); inpu t clk,rst; ou tpu t cou t1,cou t2,cou t; reg [2:0] m,n;//定义两个中间的计数变量 wire cout; reg cout1,cout2; assign cout=cout1|cout2;//将上升沿和下降沿的输出相或得到占空比为50%的波形 always @(posedge clk)//上升沿触发 begin if(rst) begin cout1<=0;m<=0;end//当 rst 为 1 时复位 else if(!rst) begin if(m==6) begin m<=0;end//计数到达 7 时计数复位 else m<=m+1;//其他情况计数器正常计数 if(m==2) cout1=~ cout1;//计数到达 3 时翻转 else if(m==5) cout1=~...