数电实验设计报告 题目: 用VHDL 语言设计一个六十进制计数器 学 院: 电子与信息工程学院 专 业: 10 级通信工程(2)班 学 号: x x x 姓 名: xx 指导老师:xxx 2012 年 6 月 5 号 一、实验目的 1

通过六十进制计数器的设计与仿真,学习 VHDL 语言及 VHDL 文本输入设计方法

编写六十进制计数器源程序,应用 MAX+Plu sII 软件进行 VHDL文本输入设计与波形仿真

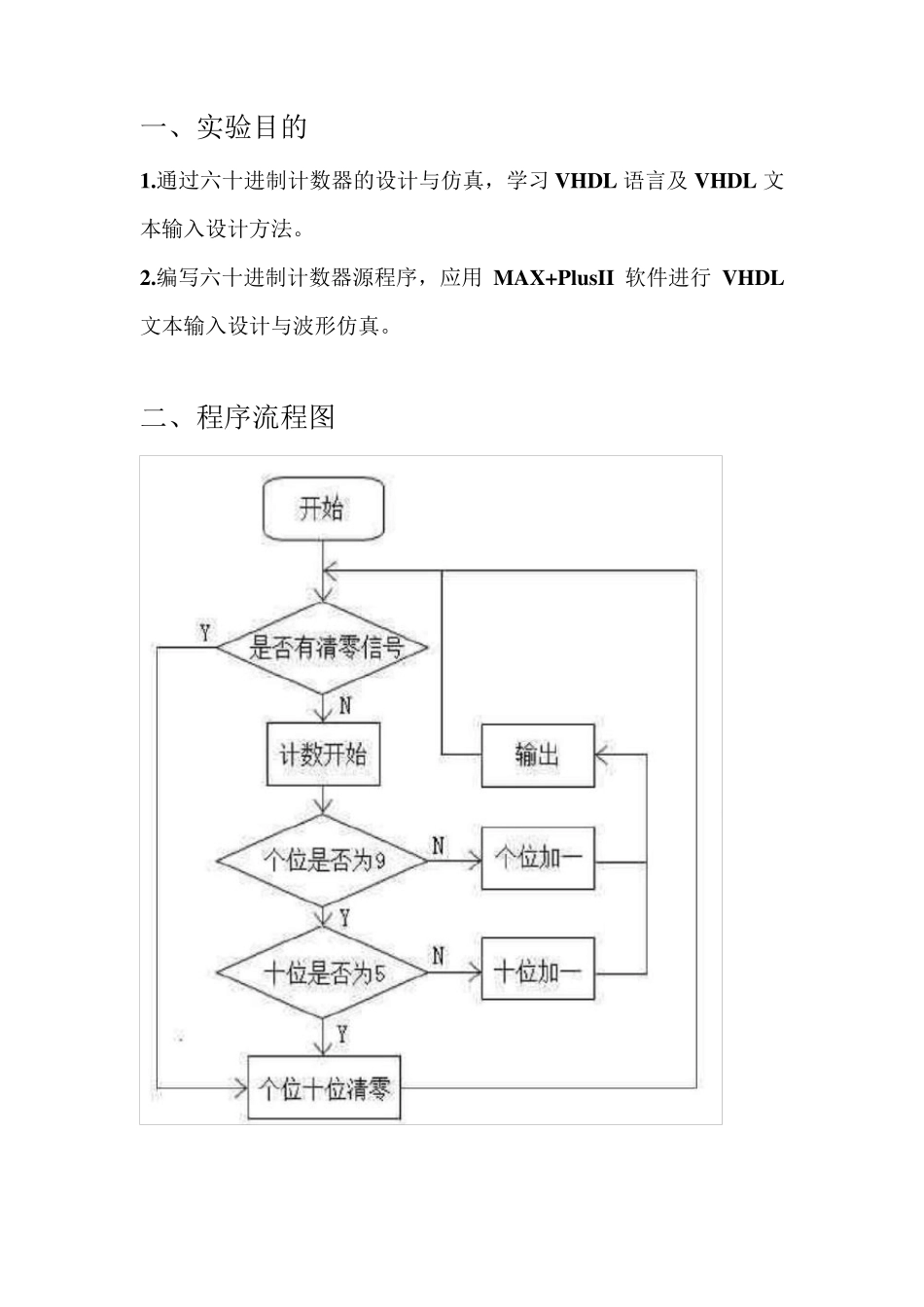

二、程序流程图 三、 程序代码及注释 library ieee; --打开 ieee 库 use ieee

std_logic_1164

all; use ieee

std_logic_arith

all; use ieee

std_logic_unsigned

all; entity count60 is --定义实体 port(en,clear,clk:in std_logic; qh:buffer std_logic_vector(3 downto 0); ql:buffer std_logic_vector(3 downto 0); Cout:out std_logic); --定义各个端口 end count60; architecture behave of count60 is begin Cout