建立工程和文件: 1、在某个盘符下新建文件夹,如D/cc 2、打开软件,新建文件File-new -VHDL File; 3、保存刚新建文件,取名为cc(最好所有文件、文件夹取名相同,以免后面编译出现错误); 4、同时软件提醒:是否建立project,选择是; 5、建立project 过程中,按软件默认设置,点击NEXT, 当到达Add File 这一步时,点击File name 右边的“

”, 然后将刚才保存的名为“cc”的文件添加进去,在点击NEXT

6、此时你已经建好了 project 和file,现在你可以在文本框中编写程序了; 注意:每次进行编译之前一定要对文件进行保存,文件名一定要和最先建立的文件夹的名字一样(cc)

编译文件、生成相应的器件: 111、编译程序 点击如图红圈圈的的按钮,即编译程序,一段时间后会显示以下对话框: 点击“确定”即编译成功

222、将我们设计的电路编译成库中的一个元件,流程如下: “File”下“Create / Update ”子菜单下的“Create sy mbol Files for Cu rrent File ”,一段时间后会出现: 点击“确认”后,即可生成相应元件

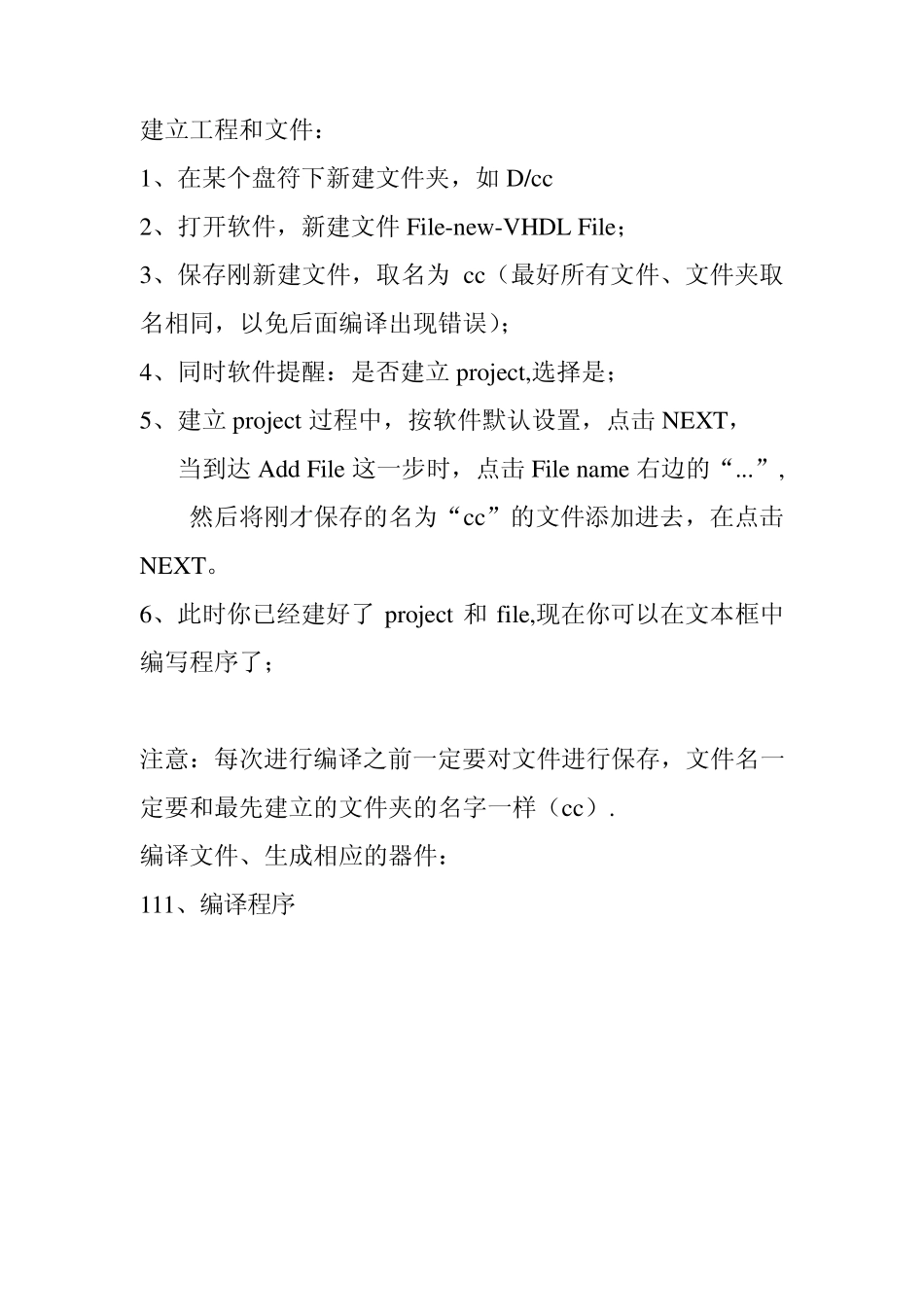

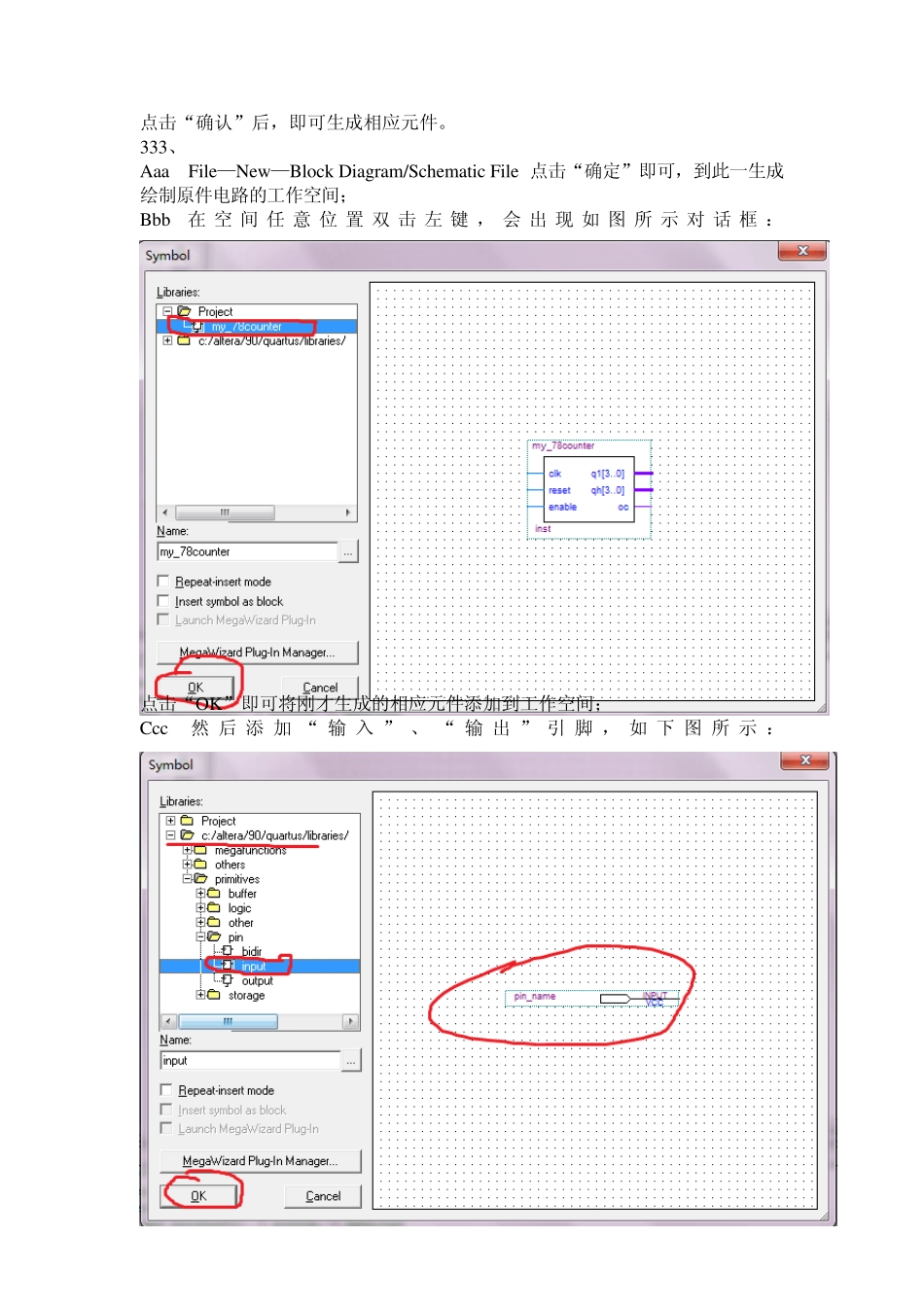

333、 Aaa File—New —Block Diagram/Schematic File 点击“确定”即可,到此一生成绘制原件电路的工作空间; Bbb在 空 间 任 意 位 置 双 击左 键 ,会 出 现 如 图 所 示 对 话 框 : 点击“OK”即可将刚才生成的相应元件添加到工作空间; Ccc 然 后添 加 “输 入 ”、“输 出 ”引 脚 ,如 下 图 所 示 : 然后将各引脚名称改为和器件上显示的一样(双击引脚,即可出现对话框) 再将引脚和器件的相应接口相连,最后结果如下: 444、保存文件,命名为cc(和先前一样) 编译,过程如下:点击