TMS320C6455 高速 SRIO 接口设计 引 言 数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领域

随着现代科技的发展,尤其是半导体工艺的进入深亚微米时代,新的功能强劲的高性能数字信号处理器(DSP)也相继推出,如 ADI(美国模拟器件)公司的 TigerSHARC 系列和 TI(德州仪器)公司的C6000 系列,但是,要实现对运算量和实时性要求越来越高的 DSP 算法,如对基于分数阶傅立叶变换的 Chirp 信号检测与估计,合成孔径雷达(SAR)成像,高频地波雷达中的自适应滤波和自适应波束形成等算法,单片 DSP 仍然显得力不从心

这些挑战主要涉及两个主题:一是计算能力,指设备、板卡和系统中分别可用的处理资源

采用多 DSP、多 FPGA 系统,将是提高运算能力的一个有效途径

二是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移

对于一些复杂的信息系统,对海量数据传输的实时性提出了苛刻的要求,多 DSP 之间、DSP 与高速 AD 采集系统、DSP 与 FPGA 间的高速数据传输,是影响信号处理流程的主要瓶颈之一

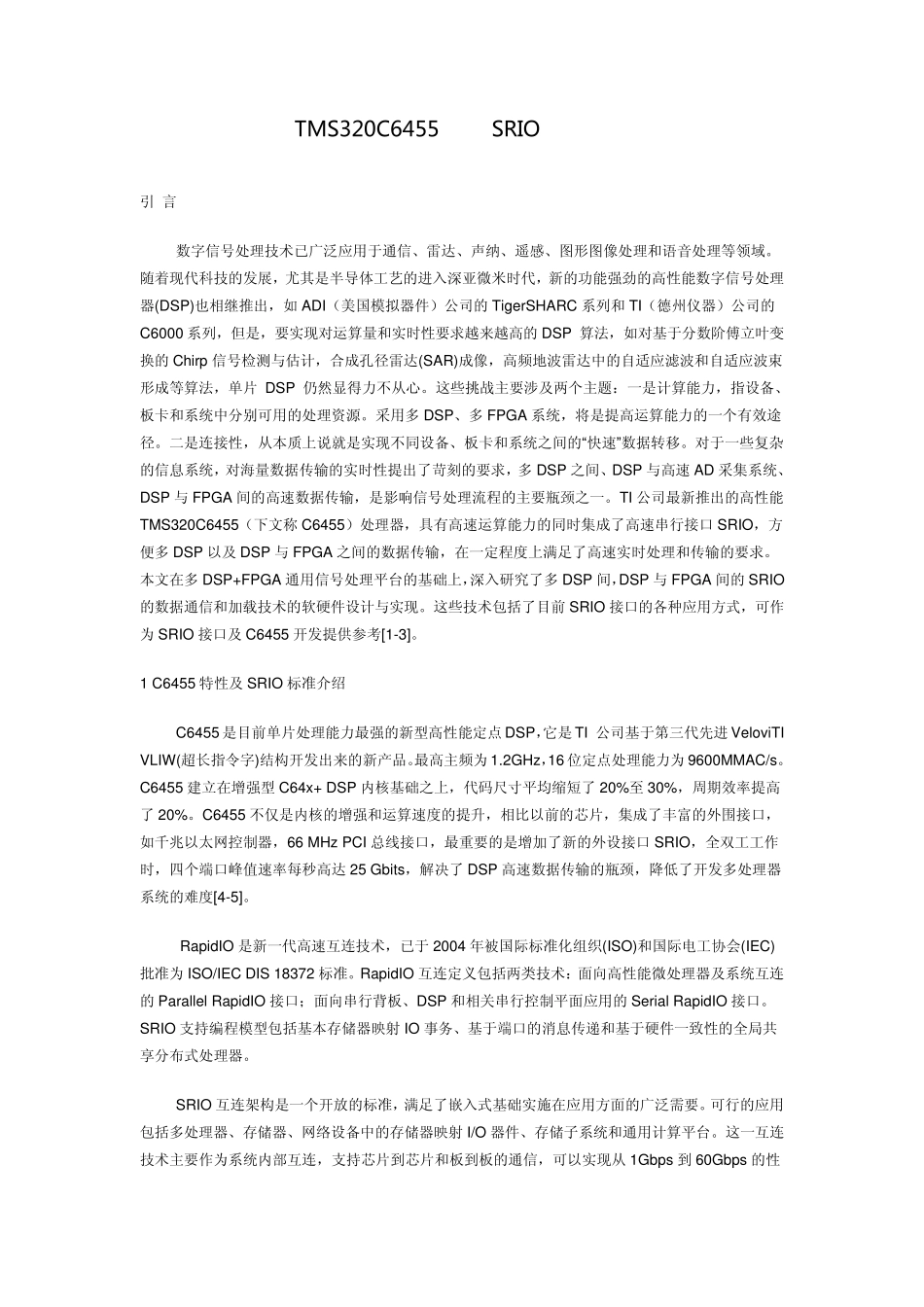

TI 公司最新推出的高性能TMS320C6455(下文称 C6455)处理器,具有高速运算能力的同时集成了高速串行接口 SRIO,方便多 DSP 以及 DSP 与 FPGA 之间的数据传输,在一定程度上满足了高速实时处理和传输的要求

本文在多 DSP+FPGA 通用信号处理平台的基础上,深入研究了多 DSP 间,DSP 与 FPGA 间的 SRIO的数据通信和加载技术的软硬件设计与实现

这些技术包括了目前 SRIO 接口的各种应用方式,可作为 SRIO 接口及 C6455 开发提供参考[1-3]

1 C6455 特性及 SRIO 标准介绍 C6455 是目前单片处理能力最强的新型高性能定点 DSP,它