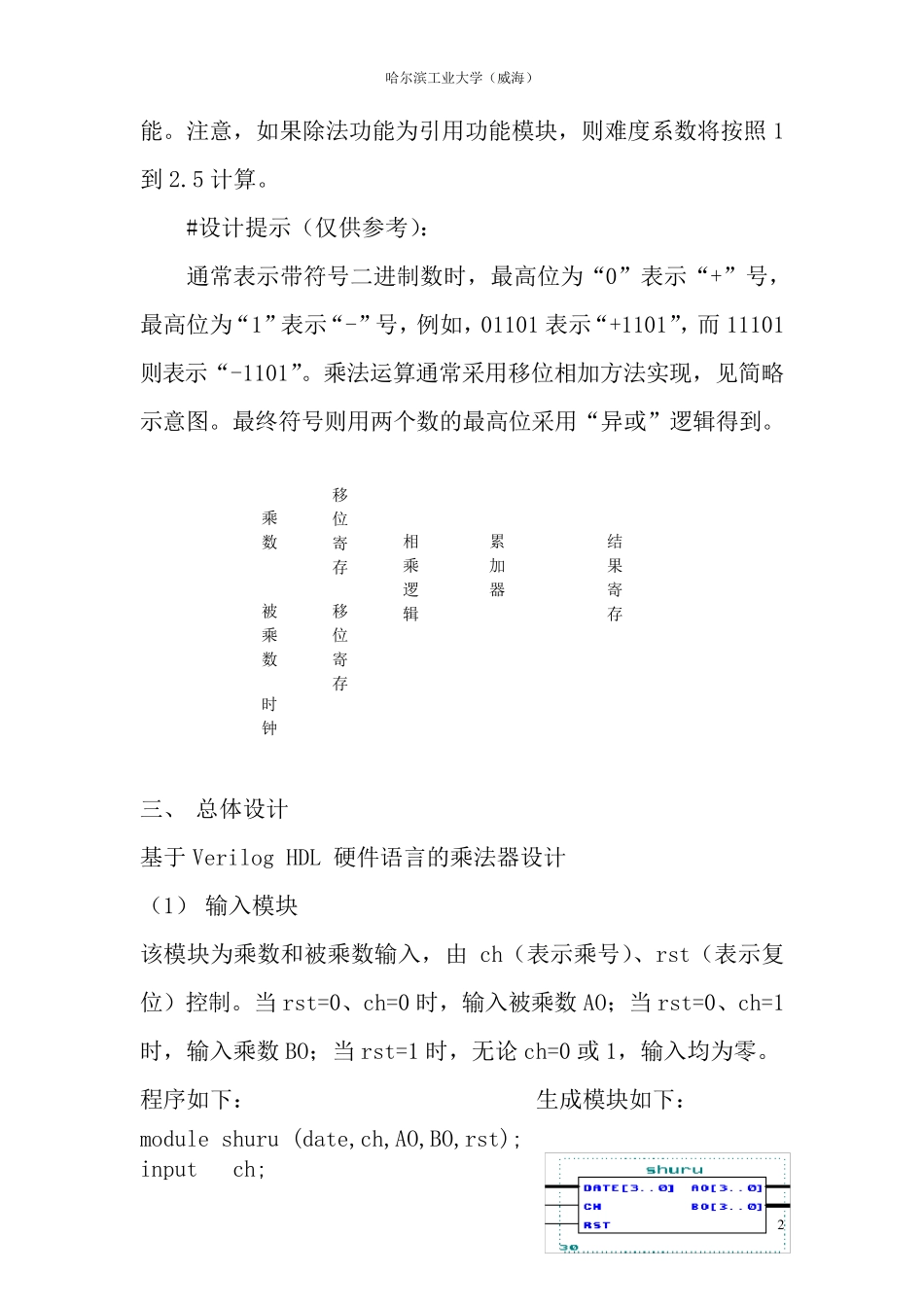

哈尔滨工业大学(威海) 0 目录 一、设计的性质、目的和任务................... 2 二、设计课题要求 ............................ 2 1、基本要求 ....................................... 2 2、 设计内容 ....................................... 2 三、总体设计 ................................ 3 1、输入模块 ....................................... 3 2、乘法模块 ....................................... 4 3、选择模块 ....................................... 5 4、显示模块 ....................................... 7 5、符号模块 ....................... 错误!未定义书签。 四、总体调试与仿真结果……………………………13 五、调试中遇到的问题及解决的方法 ........... 13 六、课程设计过程中的体会和感想 ............. 14 七、建议…………………………………………… 15 哈尔滨工业大学(威海) 1 一、 设计的性质、目的和任务 熟悉EDA 设计方法、设计语言和开发软件及设计实例,利用掌握的一种硬件描述语言(AHDL/VHDL/Verilog HDL)和EDA 开发工具(MaxPlusⅡ)进行数字系统的设计开发及仿真。通过课程设计的锻炼,要求学生掌握电路的一般设计方法,具备初步的独立设计能力,提高综合运用所学的理论知识独立分析和解决问题的能力,培养学生的创新精神。 二、 设计课题要求 (1)基本要求 掌握现代大规模集成数字逻辑电路的应用设计方法,进一步掌握电子仪器的正确使用方法,以及掌握利用计算机进行电子设计自动化(EDA)的基本方法。 (2)设计内容 设计一个两个 5 位数相乘的乘法器。用发光二极管显示输入数值,用7 段显示器显示十进制结果。乘数和被乘数分两次输入。在输入乘数和被乘数时,要求显示十进制输入数据。输入显示和计算结果显示,采用分时显示方式进行,可参见计算器的显示功哈尔滨工业大学(威海) 2 能。注意,如果除法功能为引用功能模块,则难度系数将按照1到2.5 计算。 #设计提示(仅供参考): 通常表示带符号二进制数时,最高位为“0”表示“+”号,最高位为“1”表示“-”号,例如,01101 表示“+1101”,而 11101则表示“-1101”。乘法运算通常采用移位相加方法实现,见简略示意图。最终符号则用两个数的最高位采用“异或”逻辑得到。 三、 总体设计 基于 Verilog HDL 硬件语言的乘法器设计 (1) 输入模块 该模块为...