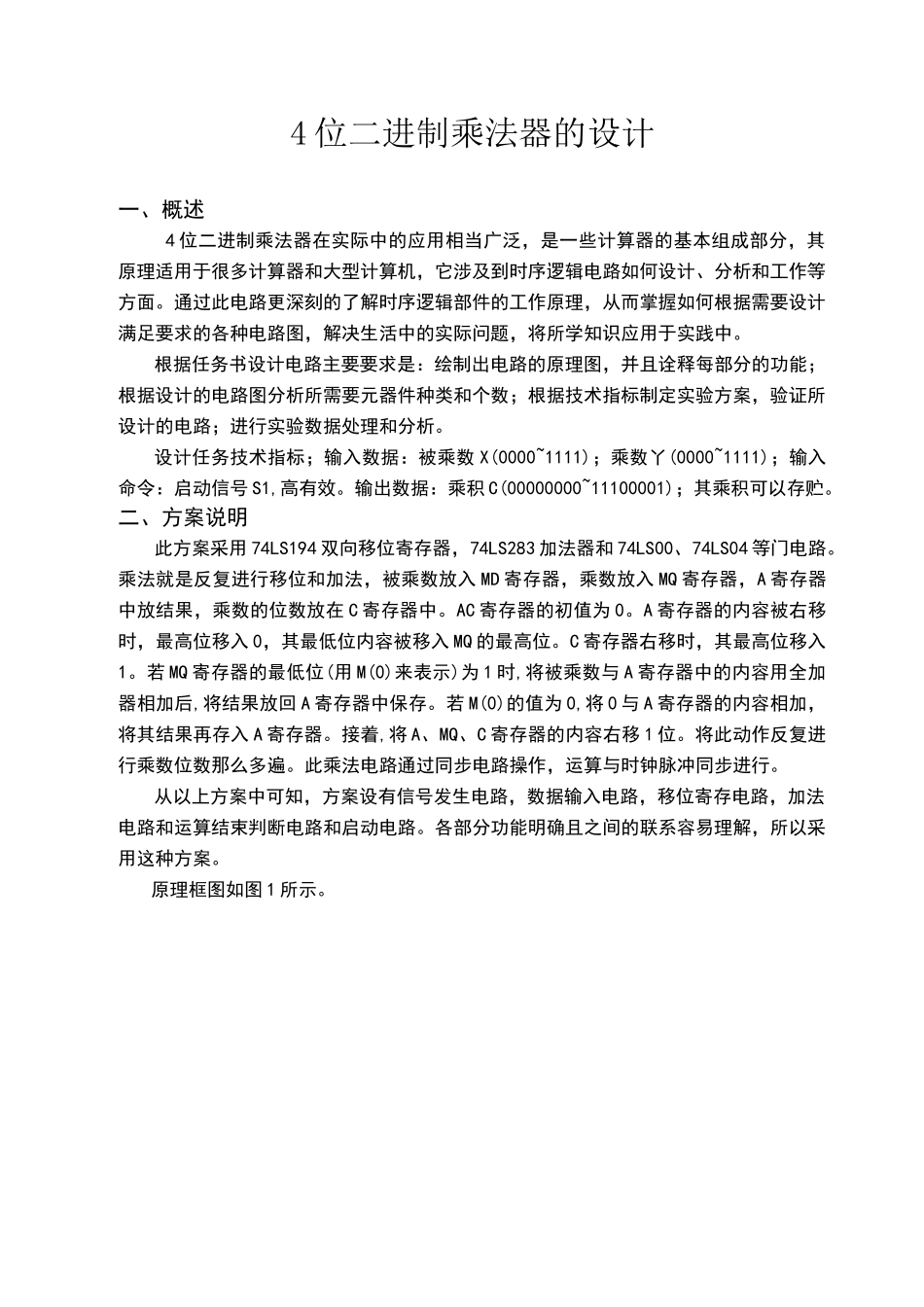

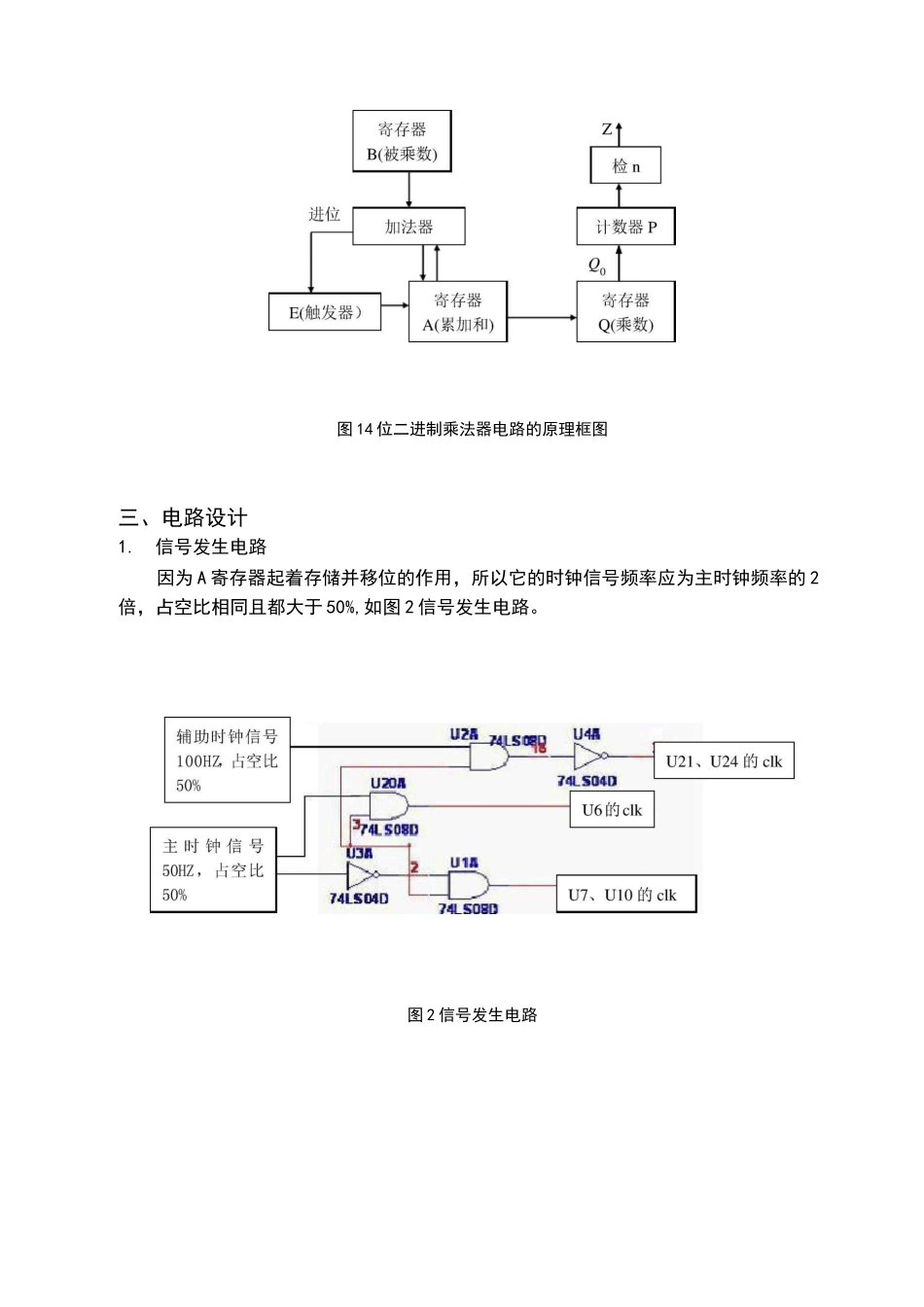

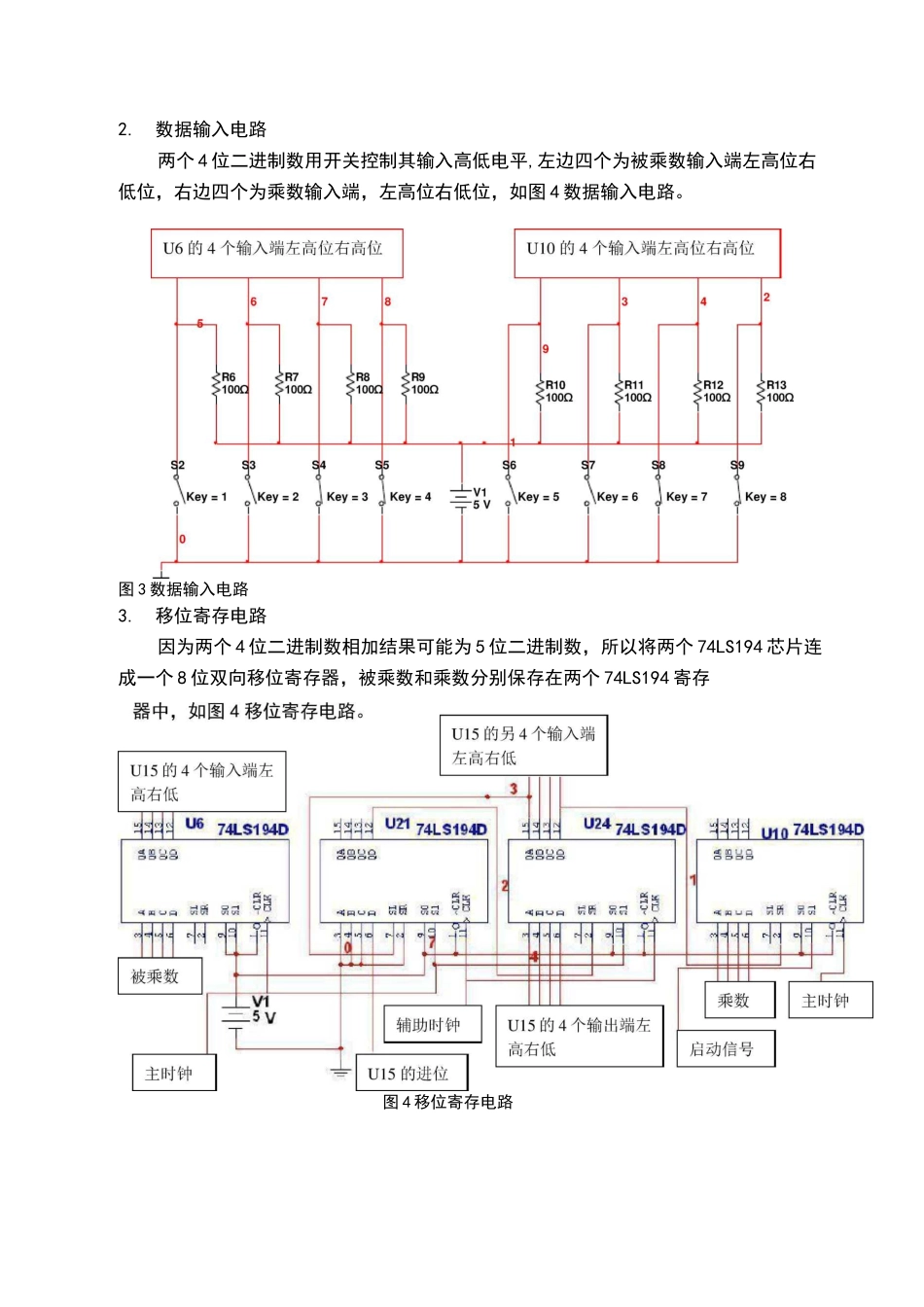

4 位二进制乘法器的设计一、概述4 位二进制乘法器在实际中的应用相当广泛,是一些计算器的基本组成部分,其原理适用于很多计算器和大型计算机,它涉及到时序逻辑电路如何设计、分析和工作等方面。通过此电路更深刻的了解时序逻辑部件的工作原理,从而掌握如何根据需要设计满足要求的各种电路图,解决生活中的实际问题,将所学知识应用于实践中。根据任务书设计电路主要要求是:绘制出电路的原理图,并且诠释每部分的功能;根据设计的电路图分析所需要元器件种类和个数;根据技术指标制定实验方案,验证所设计的电路;进行实验数据处理和分析。设计任务技术指标;输入数据:被乘数 X(0000~1111);乘数丫(0000~1111);输入命令:启动信号 S1,高有效。输出数据:乘积 C(00000000~11100001);其乘积可以存贮。二、方案说明此方案采用 74LS194 双向移位寄存器,74LS283 加法器和 74LS00、74LS04 等门电路。乘法就是反复进行移位和加法,被乘数放入 MD 寄存器,乘数放入 MQ 寄存器,A 寄存器中放结果,乘数的位数放在 C 寄存器中。AC 寄存器的初值为 0。A 寄存器的内容被右移时,最高位移入 0,其最低位内容被移入 MQ 的最高位。C 寄存器右移时,其最高位移入1。若 MQ 寄存器的最低位(用 M(0)来表示)为 1 时,将被乘数与 A 寄存器中的内容用全加器相加后,将结果放回 A 寄存器中保存。若 M(0)的值为 0,将 0 与 A 寄存器的内容相加,将其结果再存入 A 寄存器。接着,将 A、MQ、C 寄存器的内容右移 1 位。将此动作反复进行乘数位数那么多遍。此乘法电路通过同步电路操作,运算与时钟脉冲同步进行。从以上方案中可知,方案设有信号发生电路,数据输入电路,移位寄存电路,加法电路和运算结束判断电路和启动电路。各部分功能明确且之间的联系容易理解,所以采用这种方案。原理框图如图 1 所示。图 14 位二进制乘法器电路的原理框图三、电路设计1.信号发生电路因为 A 寄存器起着存储并移位的作用,所以它的时钟信号频率应为主时钟频率的 2倍,占空比相同且都大于 50%,如图 2 信号发生电路。图 2 信号发生电路2.数据输入电路两个 4 位二进制数用开关控制其输入高低电平,左边四个为被乘数输入端左高位右低位,右边四个为乘数输入端,左高位右低位,如图 4 数据输入电路。图 3 数据输入电路3.移位寄存电路因为两个 4 位二进制数相加结果可能为 5 位二进制数,所以将两个 74LS194 芯片连成一个...