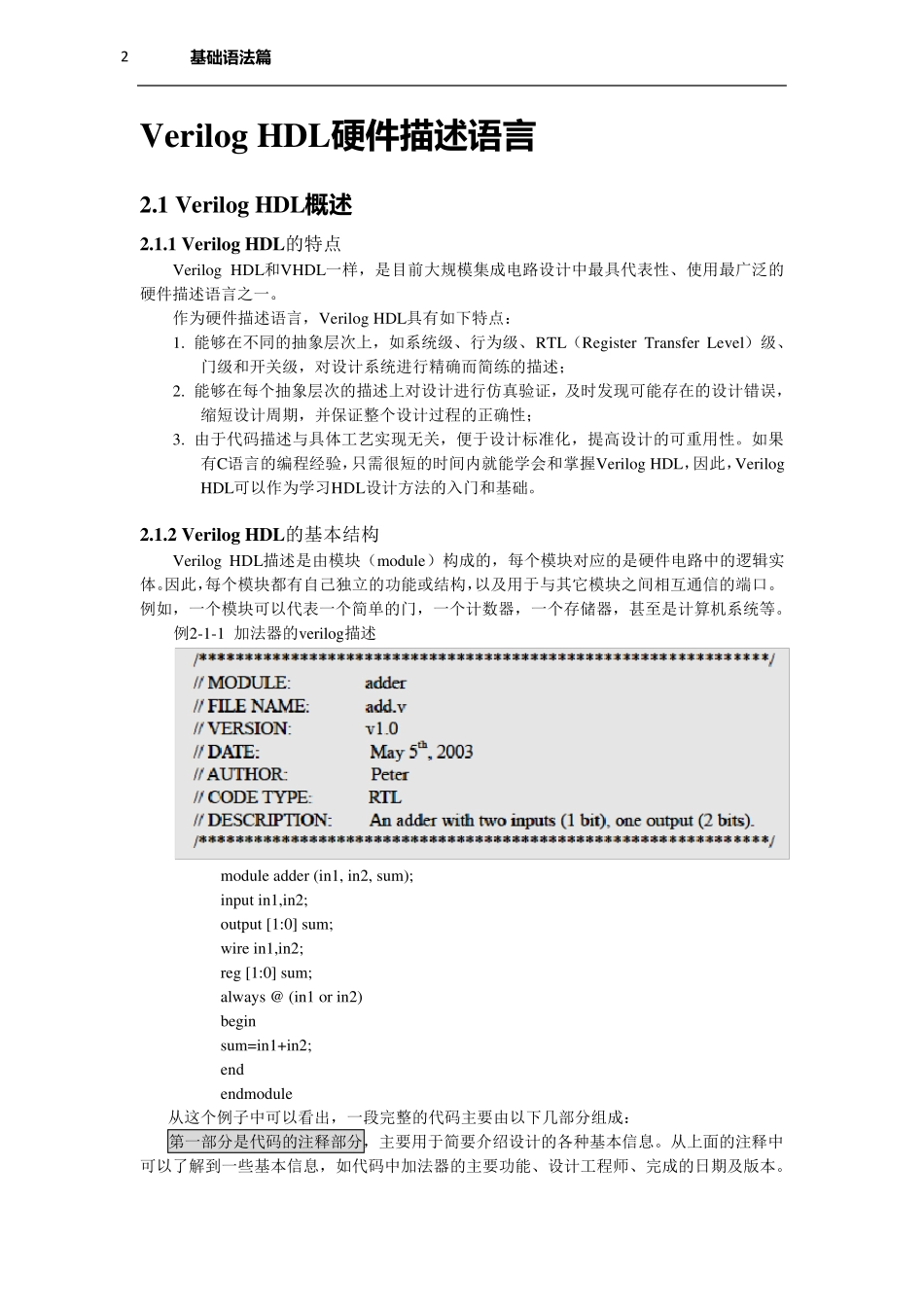

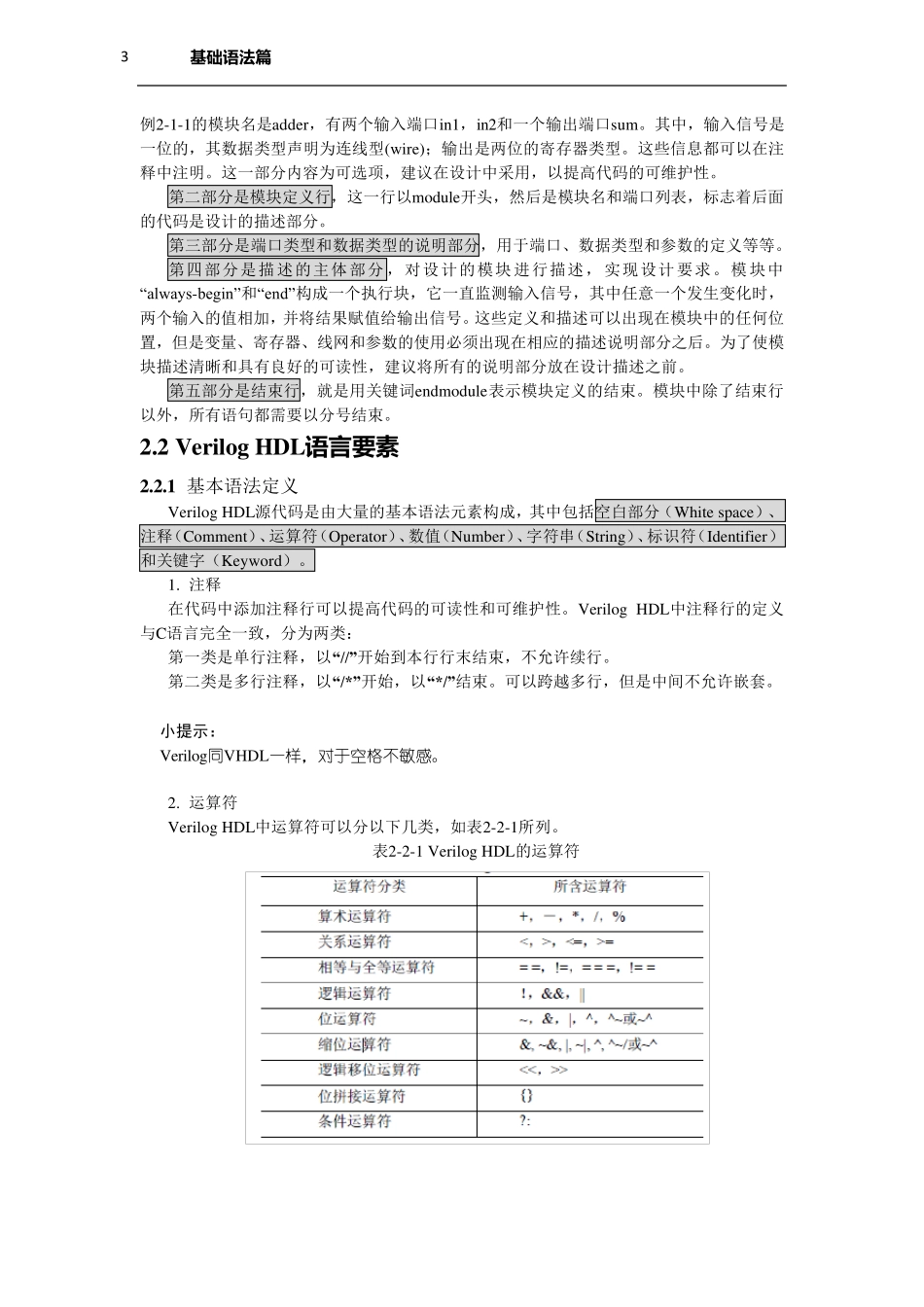

2010 HDL 基础语法篇 Verilog 2 HDL基 础 语 法 篇 Verilog Verilog HDL硬 件描述语 言 2.1 Verilog HDL概述 2.1.1 Verilog HDL的特点 Verilog HDL和VHDL一样,是目前大规模集成电路设计中最具代表性、使用最广泛的硬件描述语言之一。 作为硬件描述语言,Verilog HDL具有如下特点: 1. 能够在不同的抽象层次上,如系统级、行为级、RTL(Register Transfer Level)级、门级和开关级,对设计系统进行精确而简练的描述; 2. 能够在每个抽象层次的描述上对设计进行仿真验证,及时发现可能存在的设计错误,缩短设计周期,并保证整个设计过程的正确性; 3. 由于代码描述与具体工艺实现无关,便于设计标准化,提高设计的可重用性。如果有C语言的编程经验,只需很短的时间内就能学会和掌握Verilog HDL,因此,Verilog HDL可以作为学习HDL设计方法的入门和基础。 2.1.2 Verilog HDL的基本结构 Verilog HDL描述是由模块(module)构成的,每个模块对应的是硬件电路中的逻辑实体。因此,每个模块都有自己独立的功能或结构,以及用于与其它模块之间相互通信的端口。例如,一个模块可以代表一个简单的门,一个计数器,一个存储器,甚至是计算机系统等。 例2-1-1 加法器的verilog描述 module adder (in1, in2, sum); input in1,in2; output [1:0] sum; wire in1,in2; reg [1:0] sum; always @ (in1 or in2) begin sum=in1+in2; end endmodule 从这个例子中可以看出,一段完整的代码主要由以下几部分组成: 第一部分是代码的注释部分,主要用于简要介绍设计的各种基本信息。从上面的注释中可以了解到一些基本信息,如代码中加法器的主要功能、设计工程师、完成的日期及版本。 3 HDL基础语法篇 Verilog 例2-1-1的模块名是adder,有两个输入端口in1,in2和一个输出端口sum。其中,输入信号是一位的,其数据类型声明为连线型(wire);输出是两位的寄存器类型。这些信息都可以在注释中注明。这一部分内容为可选项,建议在设计中采用,以提高代码的可维护性。 第二部分是模块定义行,这一行以module开头,然后是模块名和端口列表,标志着后面的代码是设计的描述部分。 第三部分是端口类型和数据类型的说明部分,用于端口、数据类型和参数的定义等等。 第四部分是描述的主体 部分,对设计的模块进行描述,实现设计要求。模块中“always-begin”和“end”构成一个执行块,它一直监测输入信号...