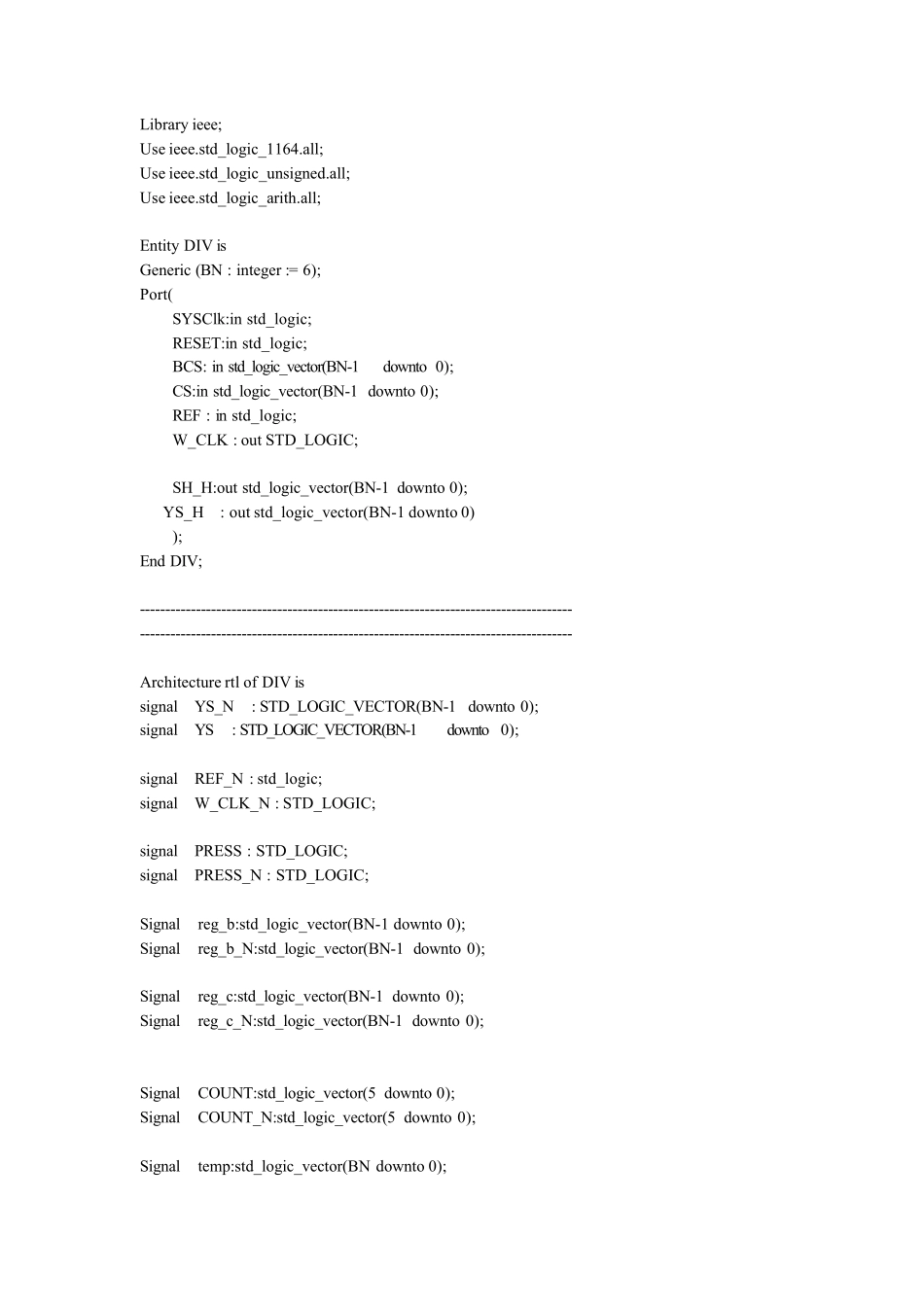

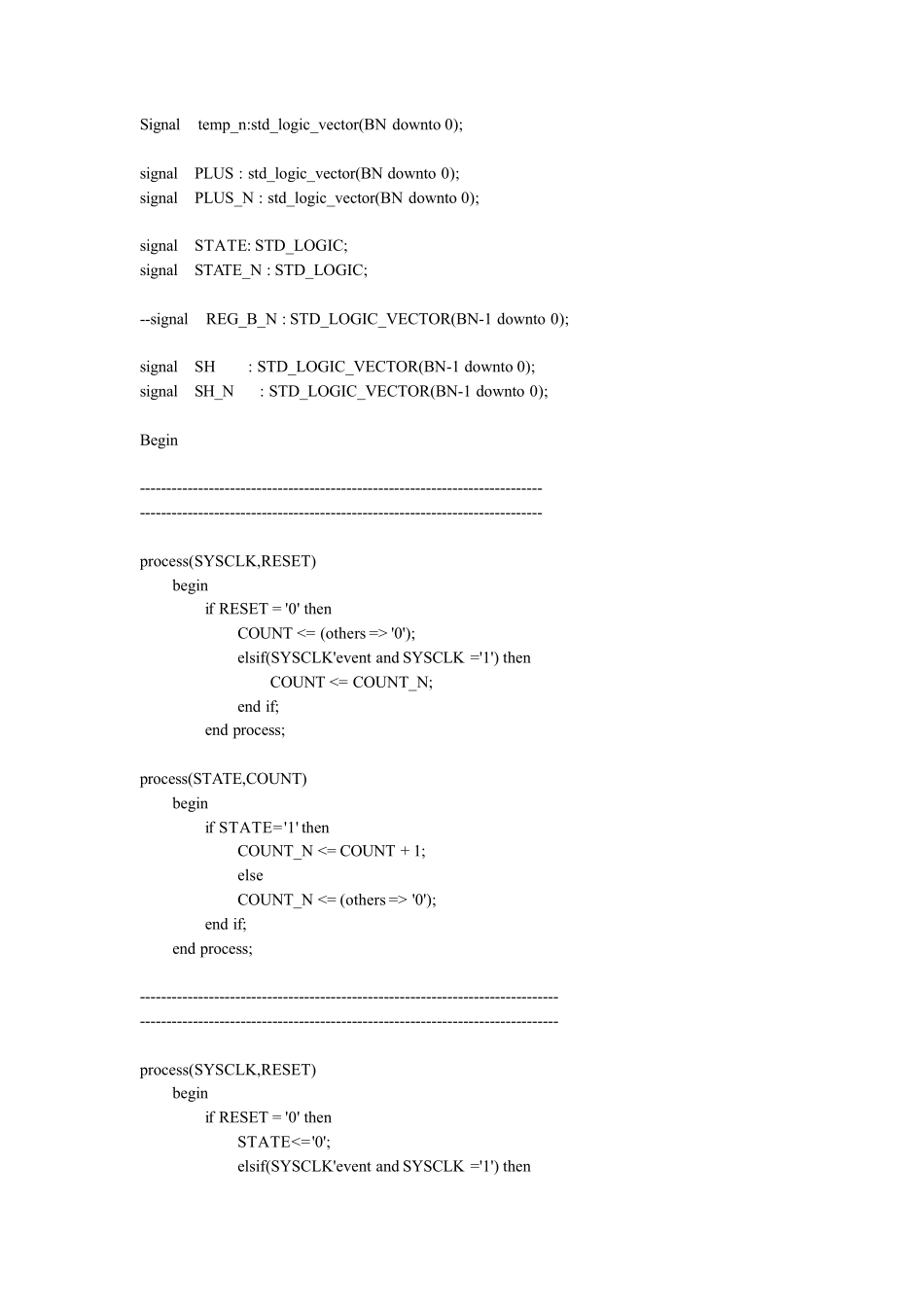

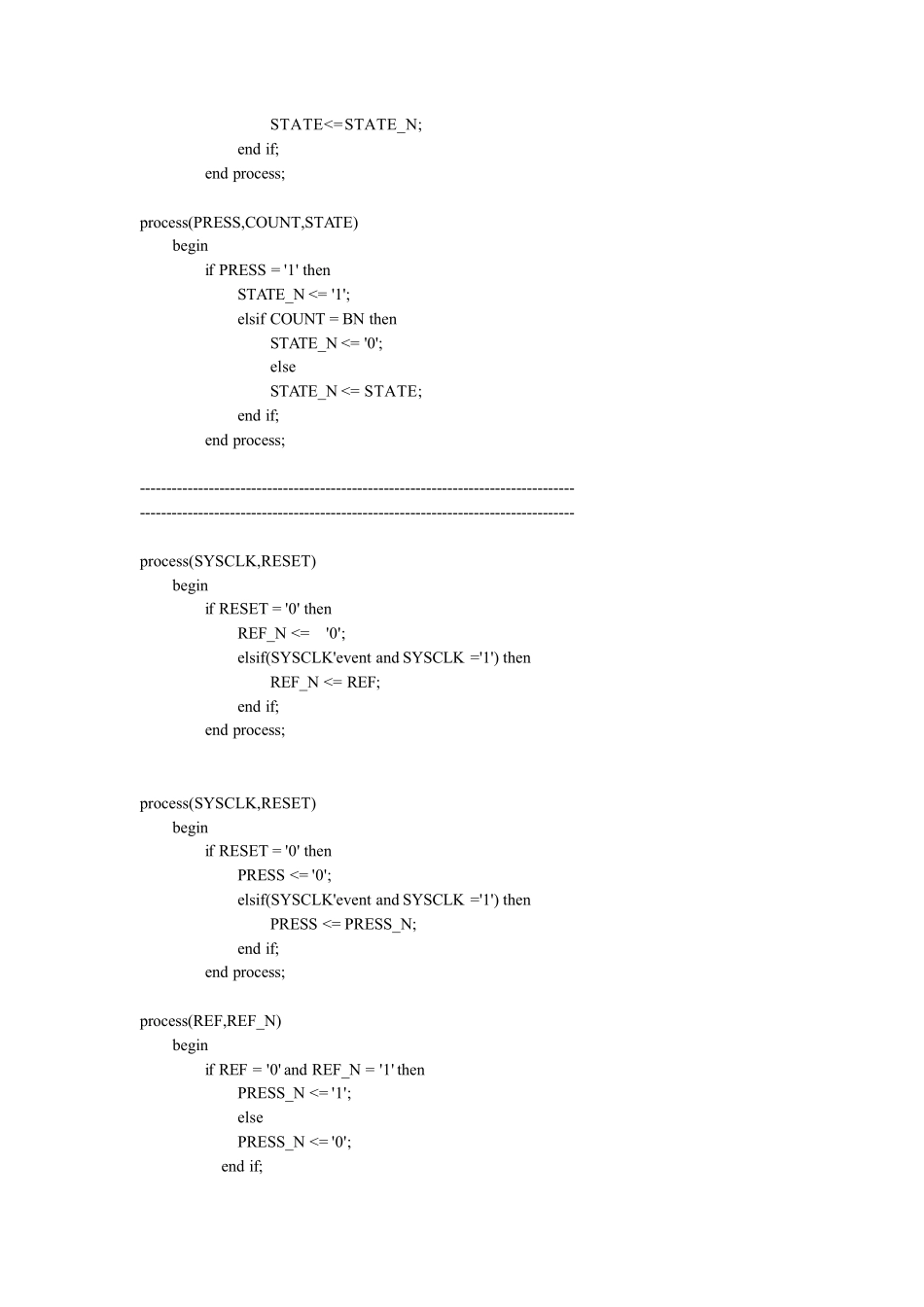

Libraryieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;EntityDIV isGeneric (BN : integer := 6);Port(SYSClk:in std_logic;RESET:in std_logic;BCS: in std_logic_vector(BN-1downto 0);CS:in std_logic_vector(BN-1 downto 0);REF : in std_logic;W_CLK : out STD_LOGIC;SH_H:out std_logic_vector(BN-1 downto 0);YS_H: out std_logic_vector(BN-1 downto 0));End DIV;--------------------------------------------------------------------------------------------------------------------------------------------------------------------------Architecture rtl of DIV issignalYS_N: STD_LOGIC_VECTOR(BN-1 downto 0);signalYS: STD_LOGIC_VECTOR(BN-1downto 0);signalREF_N : std_logic;signalW_CLK_N : STD_LOGIC;signalPRESS : STD_LOGIC;signalPRESS_N : STD_LOGIC;Signalreg_b:std_logic_vector(BN-1 downto 0);Signalreg_b_N:std_logic_vector(BN-1 downto 0);Signalreg_c:std_logic_vector(BN-1 downto 0);Signalreg_c_N:std_logic_vector(BN-1 downto 0);SignalCOUNT:std_logic_vector(5 downto 0);SignalCOUNT_N:std_logic_vector(5 downto 0);Signaltemp:std_logic_vector(BN downto 0);Signaltemp_n:std_logic_vector(BN dow nto 0);signalPLUS : std_logic_vector(BN dow nto 0);signalPLUS_N : std_logic_vector(BN dow nto 0);signalSTATE: STD_LOGIC;signalSTATE_N : STD_LOGIC;--signalREG_B_N : STD_LOGIC_VECTOR(BN-1 dow nto 0);signalSH: STD_LOGIC_VECTOR(BN-1 dow nto 0);signalSH_N: STD_LOGIC_VECTOR(BN-1 dow nto 0);Begin--------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET = '0' thenCOUNT <= (others => '0');elsif(SYSCLK'event and SYSCLK ='1') thenCOUNT <= COUNT_N;end if;end process;process(STATE,COUNT)beginif STATE='1' thenCOUNT_N <= COUNT + 1;elseCOUNT_N <= (others => '0');end if;end process;-----------------------------------------------------------...