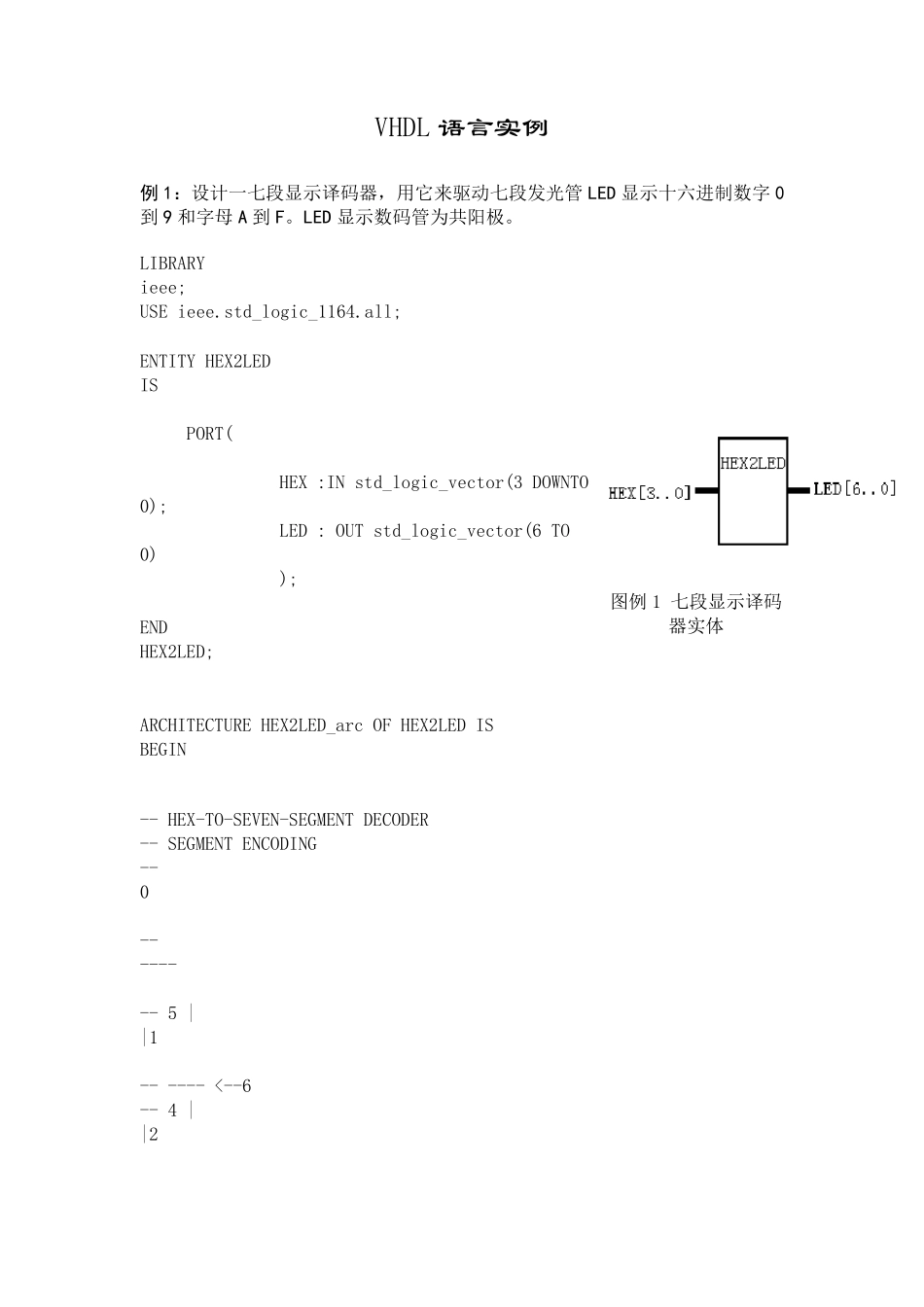

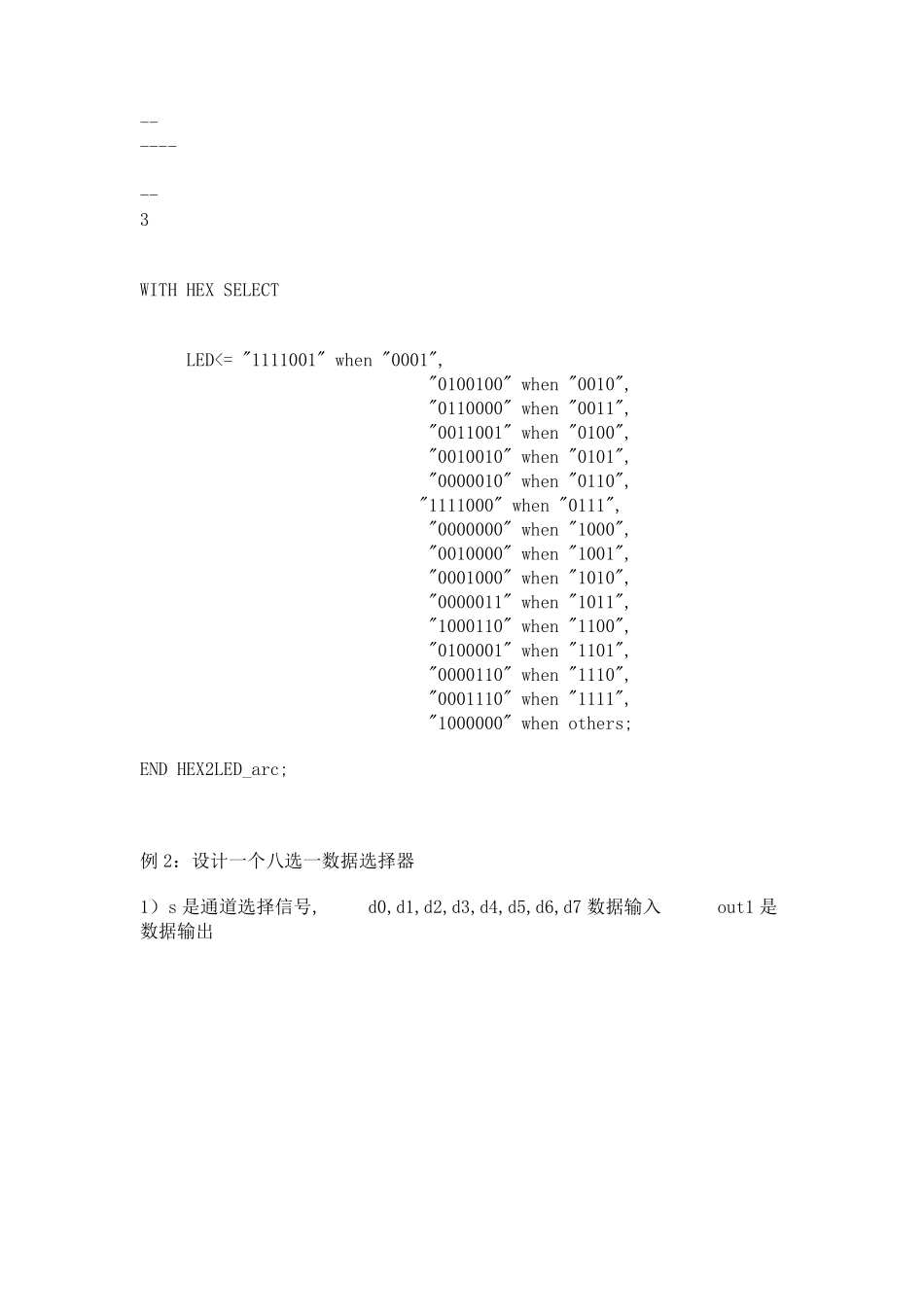

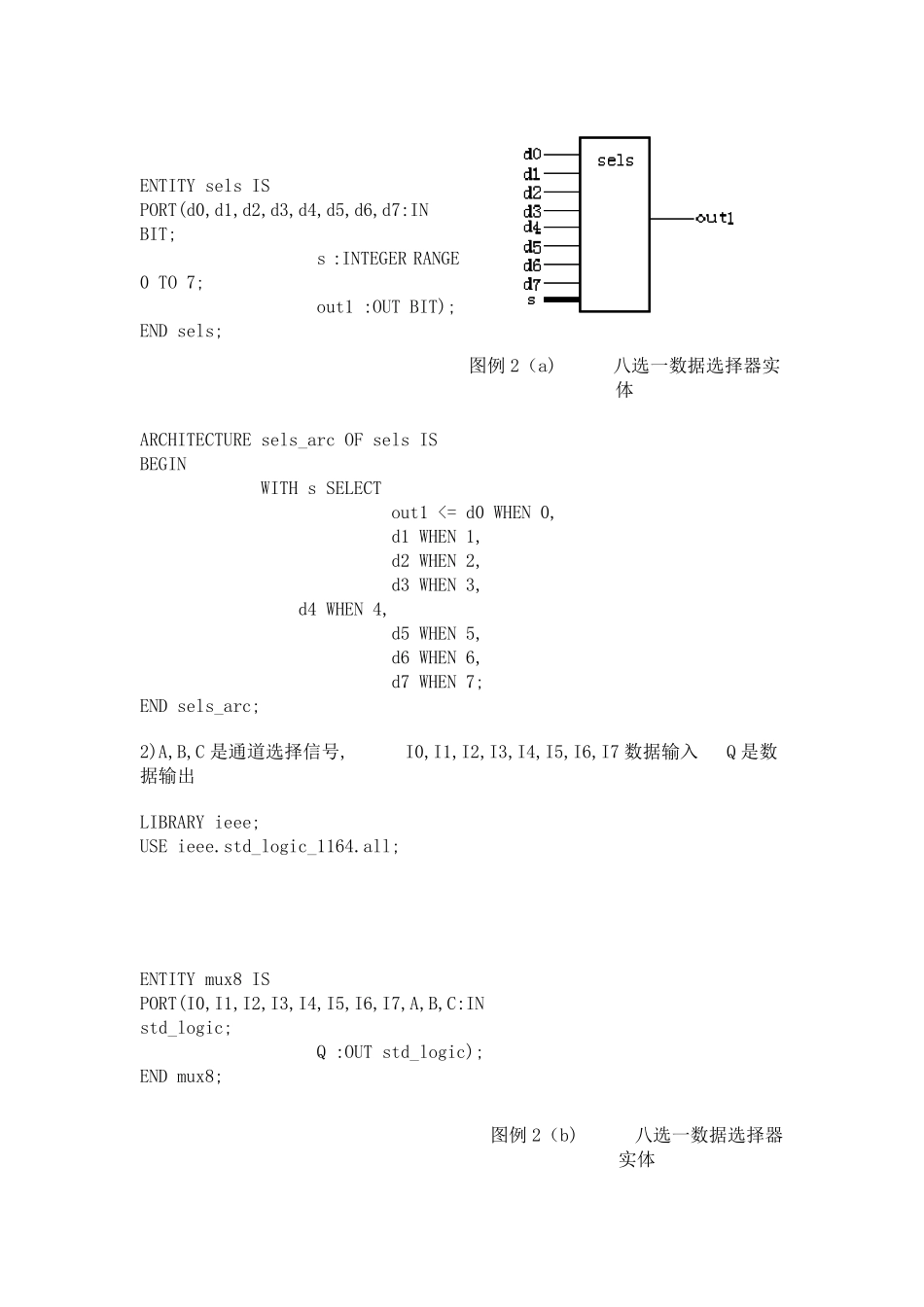

VHDL 语言实例 例 1:设计一七段显示译码器,用它来驱动七段发光管LED 显示十六进制数字0到9 和字母A 到F。LED 显示数码管为共阳极。 LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY HEX2LED IS PORT( HEX :IN std_logic_vector(3 DOWNTO 0); LED : OUT std_logic_vector(6 TO 0) ); END HEX2LED; 图例 1 七段显示译码器实体 ARCHITECTURE HEX2LED_arc OF HEX2LED IS BEGIN -- HEX-TO-SEVEN-SEGMENT DECODER -- SEGMENT ENCODING -- 0 -- ---- -- 5 | |1 -- ---- <--6 -- 4 | |2 -- ---- -- 3 WITH HEX SELECT LED<= "1111001" when "0001", "0100100" when "0010", "0110000" when "0011", "0011001" when "0100", "0010010" when "0101", "0000010" when "0110", "1111000" when "0111", "0000000" when "1000", "0010000" when "1001", "0001000" when "1010", "0000011" when "1011", "1000110" when "1100", "0100001" when "1101", "0000110" when "1110", "0001110" when "1111", "1000000" when others; END HEX2LED_arc; 例2:设计一个八选一数据选择器 1)s 是通道选择信号, d0,d1,d2,d3,d4,d5,d6,d7 数据输入 out1 是数据输出 ENTITY sels IS PORT(d0,d1,d2,d3,d4,d5,d6,d7:IN BIT; s :INTEGER RANGE 0 TO 7; out1 :OUT BIT); END sels; 图例2(a) 八选一数据选择器实体 ARCHITECTURE sels_arc OF sels IS BEGIN WITH s SELECT out1 <= d0 WHEN 0, d1 WHEN 1, d2 WHEN 2, d3 WHEN 3, d4 WHEN 4, d5 WHEN 5, d6 WHEN 6, d7 WHEN 7; END sels_arc; 2)A,B,C 是通道选择信号, I0,I1,I2,I3,I4,I5,I6,I7 数据输入 Q 是数据输出 LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY mux8 IS PORT(I0,I1,I2,I3,I4,I5,I6,I7,A,B,C:IN std_logic; Q :OUT std_logic); END mux8; 图例2(b) 八选一数据选择器实体 ARCHITECTURE mux8_arc OF mux8 IS SIGNAL sel :INTEGER ; BEGIN Q <= I0 AFTER 10 ns WHEN sel= 0 ELSE I1 AFTER 10 ns WHEN sel= 1 ELSE I2 AFTER 10 ns WHEN sel= 2 ELSE I3 AFTER 10 ns WHEN sel= 3 ELSE I4 AFTER 10 ns WHEN sel= 4 ELSE I5 AFTER 1...