数字电子技术课程设计-- 简易电子琴设计专业班级:电子姓名:学号:日期: 2015

5 一、设计任务用 VerilogHDL 语言设计简易电子琴

(1)单独从左至右按下S1-S7 每个按键后能够各自对应发出“哆来咪发唆啦西”的音乐声;(2)按下最右边按键( S8),同时再配合按下S1-S7键后,发高八度的对应音;(3)按键需要进行“消抖”处理;(4)外部输入脉冲信号频率为1mhz;(5)扩展要求:自主设计(增加低8 度功能)

二、实验目的1、学习 verilogHDL 语言的基本运用,能够利用其进行简单编程;2、学习使用 Quartus Ⅱ7

0 的基本操作,能够利用其进行简单的设计;3、结合实践加深对理论知识的理解

三、设计原理1)喇叭的振动频率不同,导致产生不同的声音;振动频率越低,声音越低沉,振动频率越高,声音越尖锐

题目中音乐基本音的“哆”对应频率为523Hz、“来”对应频率为587Hz、“咪”对应频率为 659Hz、“发”对应频率为698Hz、“唆”对应频率为784Hz、“啦”对应频率为880Hz、“西”对应频率为 998Hz

低 8 度音:基本音频率 /2 ,例如低音 1 的频率为 523/2=261

高 8 度音:基本音频率× 2,例如高音 1 的频率为 523×2=1046Hz

不同的频率产生利用给定的时钟脉冲来进行分频实现

(2)消抖的原理:按键默认输入逻辑‘1’,当有按键按下时对应的输入为逻辑‘0’(但会存在抖动),当 FPGA开始检测到该引脚从‘ 1’变为‘ 0’后开始定时(按键抖动时间大约10ms),定时时间结束后若该引脚仍然为‘0’则表示确实发生按键按下,否则视为抖动而不予以理会;按键松开过程的消抖处理和按下时原理一样

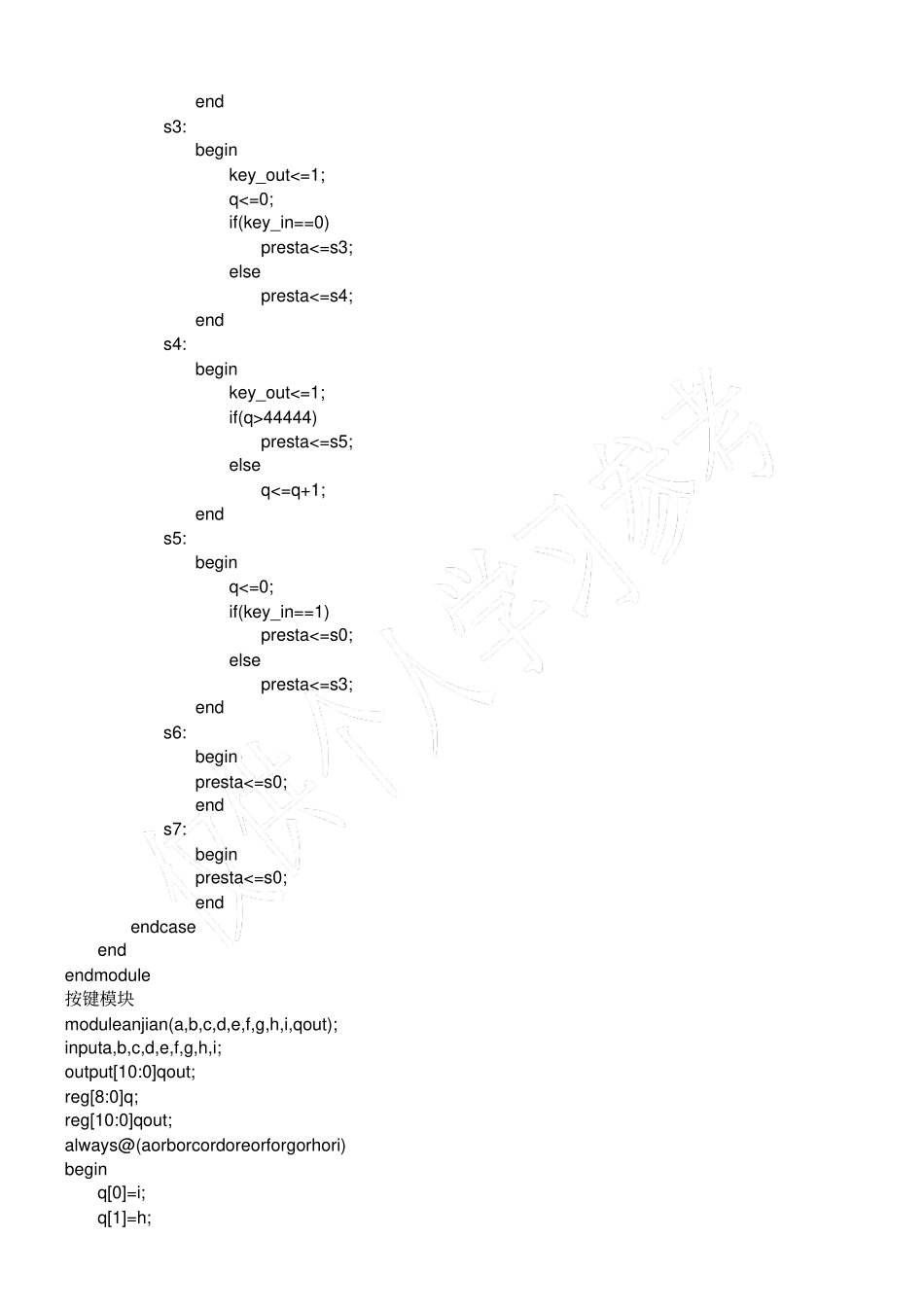

(3)原理框图四、程序设计消抖模块modulexiaodou(key_in,key_out,clk); inputk