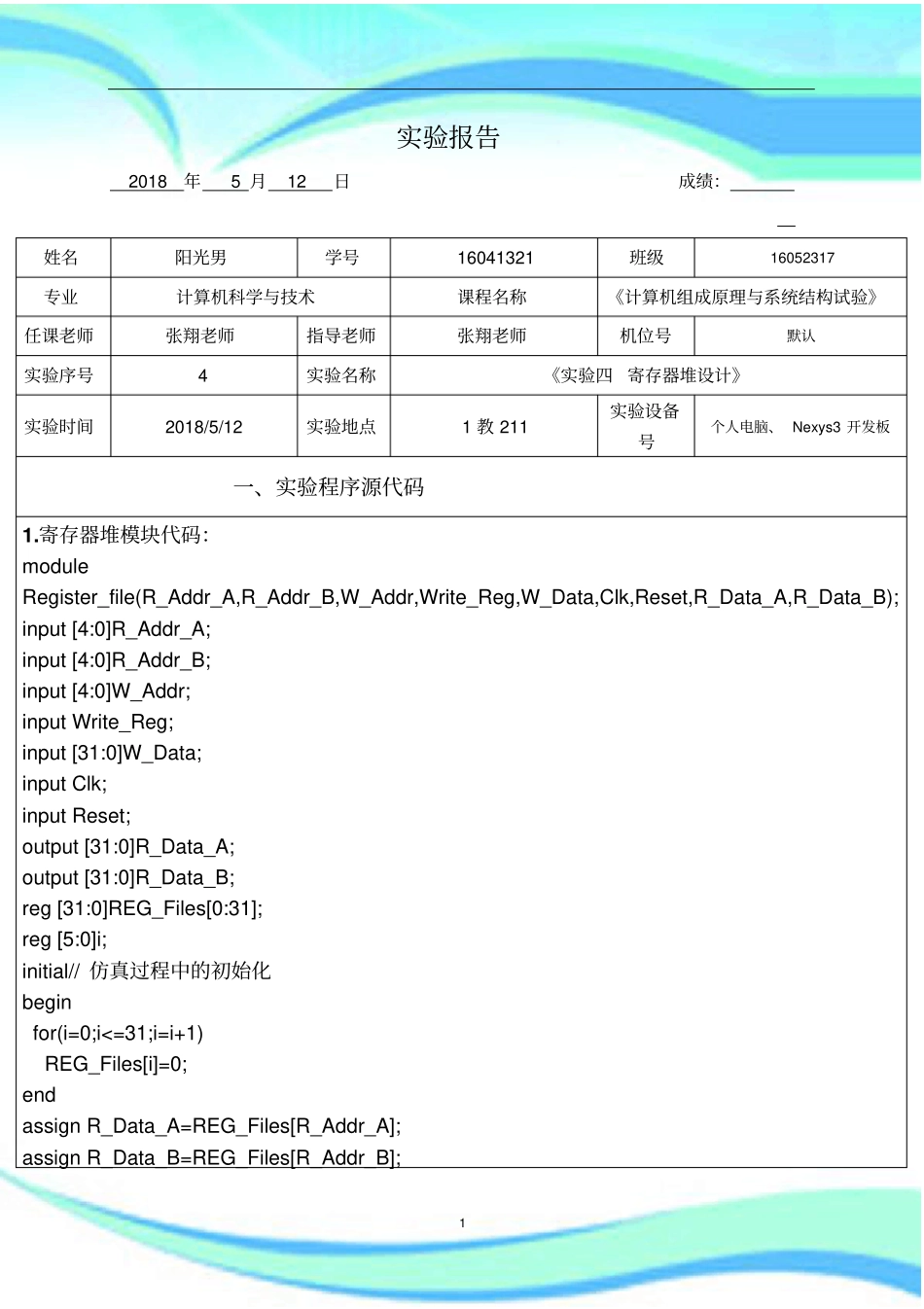

杭电计组实验 - 寄存器堆设计实验2 ————————————————————————————————作者:————————————————————————————————日期:1 实验报告2018 年5 月12 日成绩:姓名阳光男学号16041321 班级16052317 专业计算机科学与技术课程名称《计算机组成原理与系统结构试验》任课老师张翔老师指导老师张翔老师机位号默认实验序号4 实验名称《实验四寄存器堆设计》实验时间2018/5/12 实验地点1 教 211 实验设备号个人电脑、 Nexys3 开发板一、实验程序源代码1

寄存器堆模块代码:module Register_file(R_Addr_A,R_Addr_B,W_Addr,Write_Reg,W_Data,Clk,Reset,R_Data_A,R_Data_B); input [4:0]R_Addr_A; input [4:0]R_Addr_B; input [4:0]W_Addr; input Write_Reg; input [31:0]W_Data; input Clk; input Reset; output [31:0]R_Data_A; output [31:0]R_Data_B; reg [31:0]REG_Files[0:31]; reg [5:0]i; initial// 仿真过程中的初始化begin for(i=0;i