实验三加法器的设计与仿真一、实验目的熟悉QuartusⅡ仿真软件的基本操作,用逻辑图和VHDL语言设计加法器并验证

二、实验内容1、熟悉QuartusⅡ软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)2、用逻辑图和VHDL语言设计全加器并进行仿真验证;3、用设计好的全加器组成串行加法器并进行仿真验证;4、用逻辑图设计4位先行进位全加器并进行仿真验证;三、实验原理1

全加器全加器英文名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器

一位全加器可以处理低位进位,并输出本位加法进位

多个一位全加器进行级联可以得到多位全加器

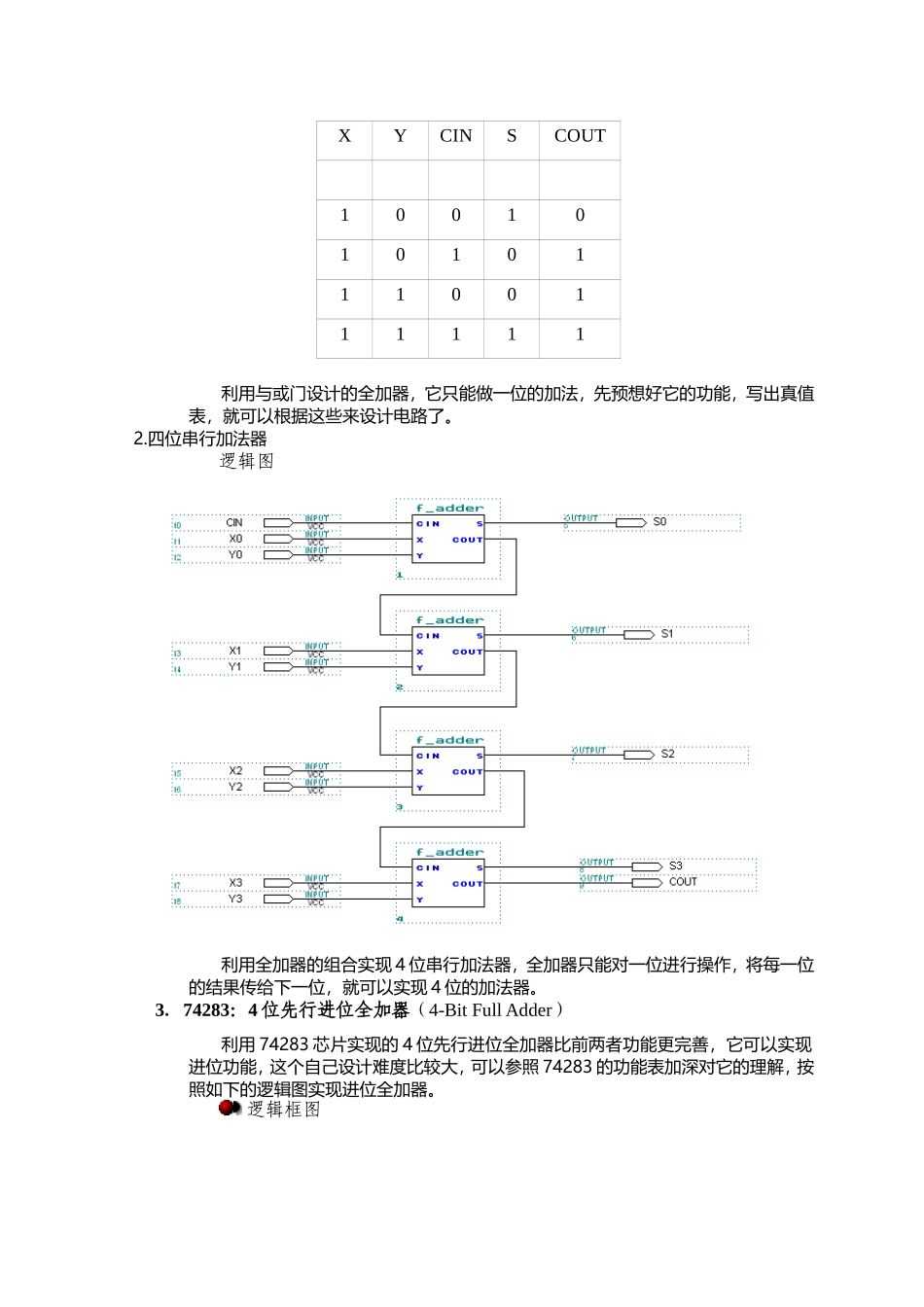

用途:实现一位全加操作逻辑图真值表XYCINSCOUT00000001100101001101XYCINSCOUT10010101011100111111利用与或门设计的全加器,它只能做一位的加法,先预想好它的功能,写出真值表,就可以根据这些来设计电路了

四位串行加法器逻辑图利用全加器的组合实现4位串行加法器,全加器只能对一位进行操作,将每一位的结果传给下一位,就可以实现4位的加法器

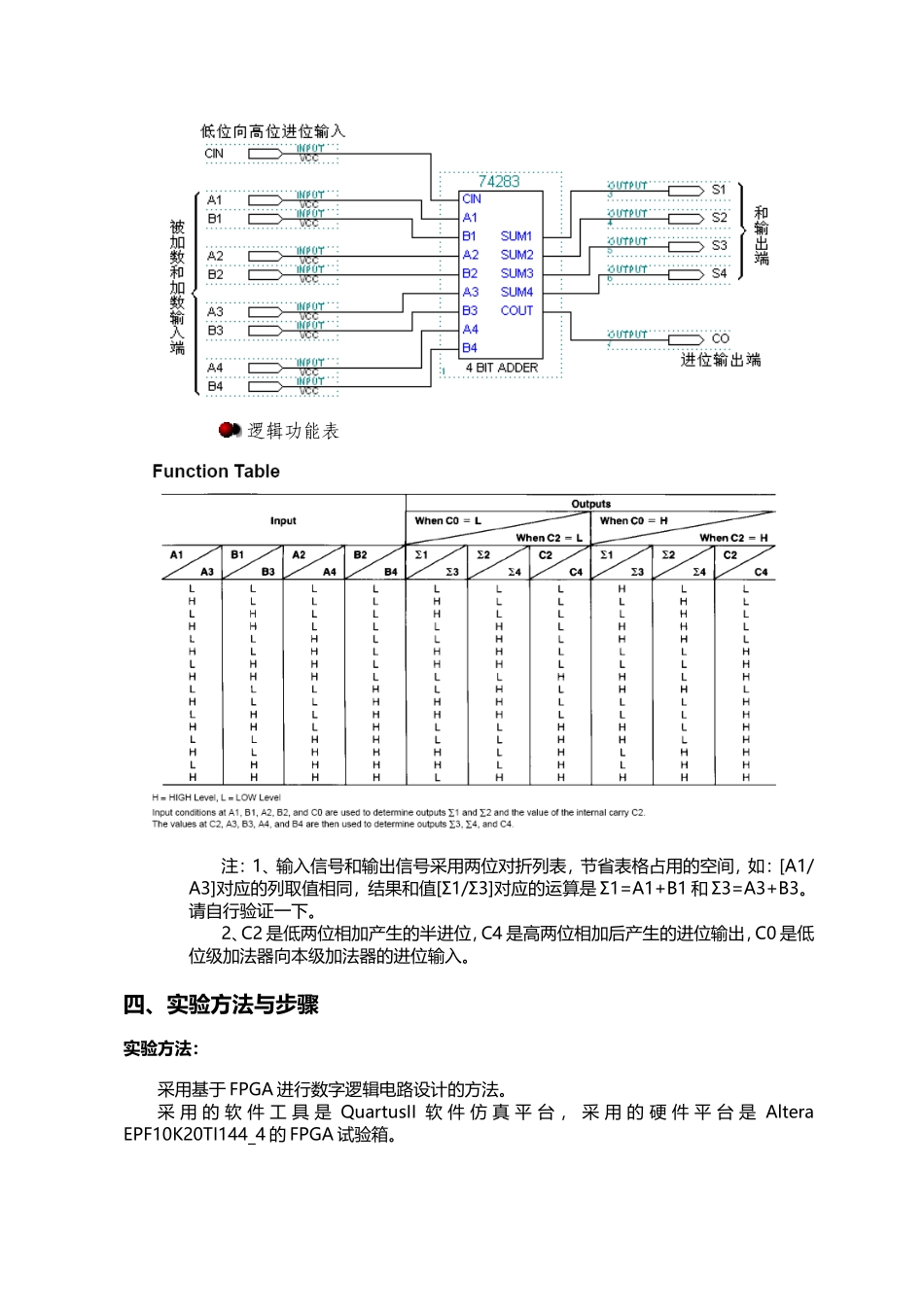

3.74283:4位先行进位全加器(4-BitFullAdder)利用74283芯片实现的4位先行进位全加器比前两者功能更完善,它可以实现进位功能,这个自己设计难度比较大,可以参照74283的功能表加深对它的理解,按照如下的逻辑图实现进位全加器

逻辑框图逻辑功能表注:1、输入信号和输出信号采用两位对折列表,节省表格占用的空间,如:[A1/A3]对应的列取值相同,结果和值[Σ1/Σ3]对应的运算是Σ1=A1+B1和Σ3=A3+B3

请自行验证一下

2、C2是低两位相加产生的半进位,C4是高两位相加后产生的进位输出,C0是低位级加法器向本级加法器的进位输入

四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电