基于 multisim 10

0的数字时钟仿真设计 一、设计目的 1、综合运用数字电路的知识,掌握数字时钟的设计方法

2、掌握计数器、译码器、分频器的设计原理和设计方法

3、掌握运用仿真软件 multisim 10

0设计综合数字电路的方法

二、设计意义 数字时钟是用数字集成电路构成的、用数码显示的一种现代计时器,与传统机械表相比,它具有走时准确、校时方便、显示直观、无机械传动装置等特点,因而广泛应用于车站、码头、机场、商店等公共场所

在控制系统中,数字时钟也常用来做定时控制的时钟源

三、设计要求 1、设计一个具有时、分、秒的十进制数字显示的计时器

2、具有手动校时、校分的功能

3、通过开关能实现小时的十二进制和二十四进制转换

4、具有整点报时的功能

5、用 74系列集成电路设计实现 6、电路实现的各功能部分用子电路表示

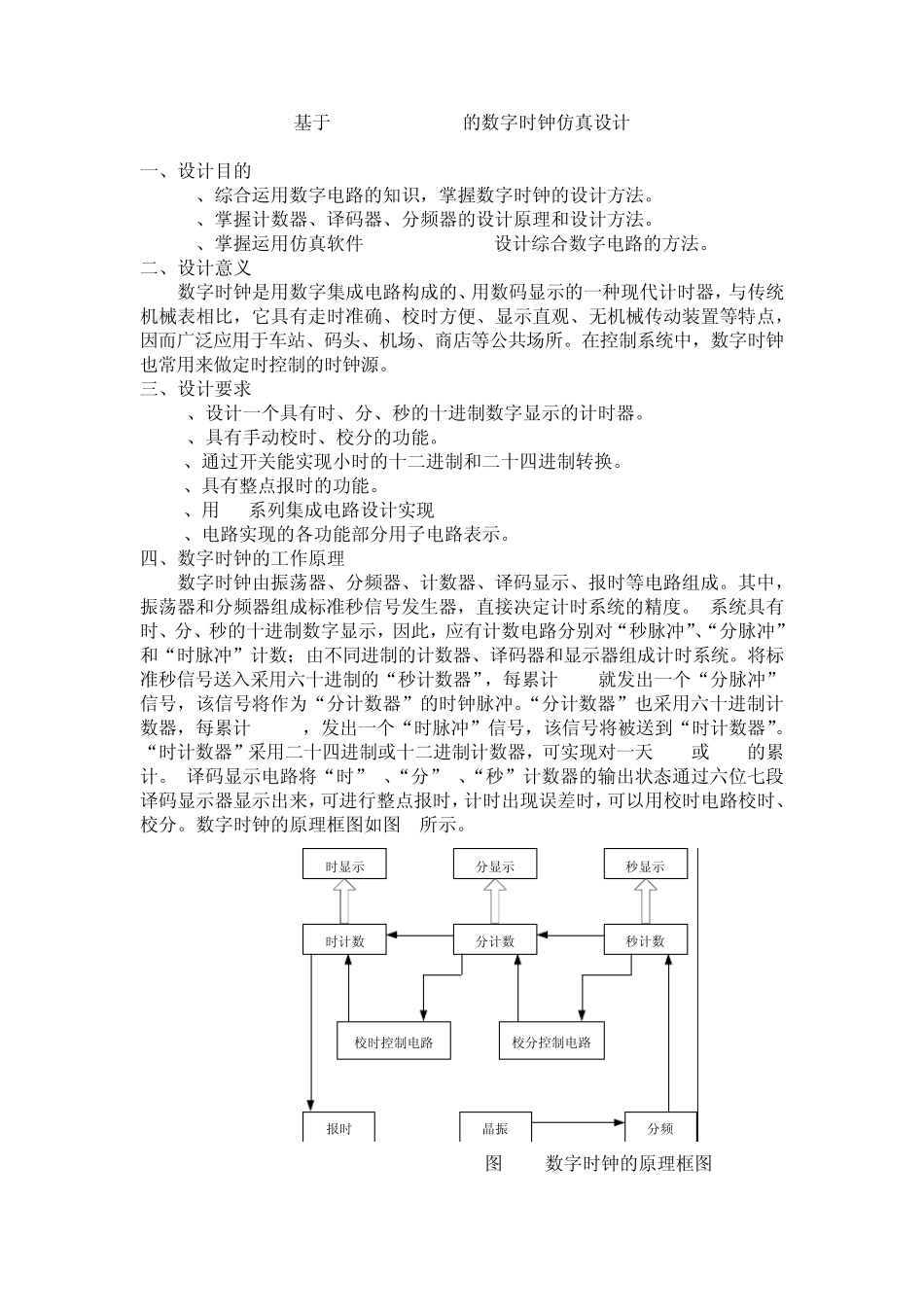

四、数字时钟的工作原理 数字时钟由振荡器、分频器、计数器、译码显示、报时等电路组成

其中,振荡器和分频器组成标准秒信号发生器,直接决定计时系统的精度

系统具有时、分、秒的十进制数字显示,因此,应有计数电路分别对“秒脉冲”、“分脉冲”和“时脉冲”计数;由不同进制的计数器、译码器和显示器组成计时系统

将标准秒信号送入采用六十进制的“秒计数器”,每累计 60s就发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲

“分计数器”也采用六十进制计数器,每累计 60min,发出一个“时脉冲”信号,该信号将被送到“时计数器”

“时计数器”采用二十四进制或十二进制计数器,可实现对一天 24h或 10h的累计

译码显示电路将“时” 、“分” 、“秒”计数器的输出状态通过六位七段译码显示器显示出来,可进行整点报时,计时出现误差时,可以用校时电路校时、校分

数字时钟的原理框图如图 1所示

时显示秒显示分显示时计数分计数秒计数校时控制电路校分控制电路